Datasheet Summary

..

DATA SHEET

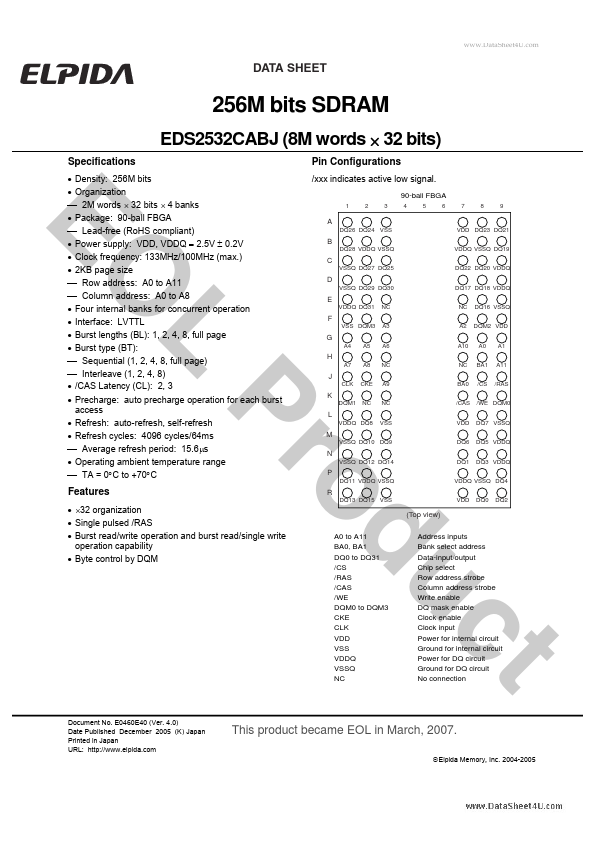

256M bits SDRAM

EDS2532CABJ (8M words × 32 bits)

Specifications

- Density: 256M bits

- Organization ⎯ 2M words × 32 bits × 4 banks

- Package: 90-ball FBGA ⎯ Lead-free (RoHS pliant)

- Power supply: VDD, VDDQ = 2.5V ± 0.2V

- Clock frequency: 133MHz/100MHz (max.)

- 2KB page size ⎯ Row address: A0 to A11 ⎯ Column address: A0 to A8

- Four internal banks for concurrent operation

- Interface: LVTTL

- Burst lengths (BL): 1, 2, 4, 8, full page

- Burst type (BT): ⎯ Sequential (1, 2, 4, 8, full page) ⎯ Interleave (1, 2, 4, 8)

- /CAS Latency (CL): 2, 3

- Precharge: auto precharge operation for each burst access

- Refresh: auto-refresh, self-refresh

- Refresh cycles:...