EDS2532EESL-75

EDS2532EESL-75 is 256M bits SDRAM manufactured by Elpida Memory.

Features

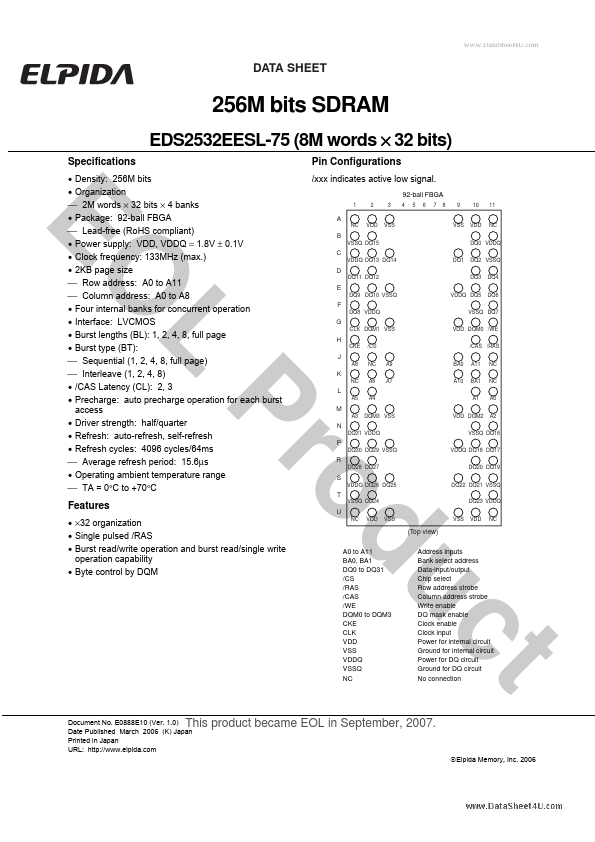

VSSQ DQ15 DQ0 VDDQ DQ1 DQ2 VSSQ DQ3 VDDQ DQ5 DQ4 DQ6

VDDQ DQ13 DQ14

DQ11 DQ12

DQ9 DQ10 VSSQ

DQ8 VDDQ VSSQ DQ7 VDD DQM0 /WE /CAS /RAS A9 A7 BA0 A10 A11 BA1 A1 VDD DQM2 NC NC A0 A2

CLK DQM1 VSS

- ×32 organization

- Single pulsed /RAS

- Burst read/write operation and burst read/single write operation capability

- Byte control by DQM

Document No. E0888E10 (Ver. 1.0) Date Published March 2006 (K) Japan Printed in Japan URL: http://.elpida.

CKE /CS NC A6 A4 DQM3 VSS

A8

A5

This product became EOL in September, 2007.

Elpida Memory, Inc. 2006

Pr

M N P R S T U

A3

DQ31 VDDQ DQ30 DQ29 VSSQ DQ28 DQ27

VSSQ DQ16 VDDQ DQ18 DQ17 DQ20 DQ19 DQ22 DQ21 VSSQ DQ23 VDDQ VSS VDD NC

VDDQ DQ26 DQ25 VSSQ DQ24 NC VDD od

(Top view) Address inputs Bank select address Data-input/output Chip select Row address strobe Column address strobe Write enable DQ mask enable Clock enable Clock input Power for internal circuit Ground for internal circuit Power for DQ circuit Ground for DQ circuit No connection

A0 to A11 BA0, BA1 DQ0 to DQ31 /CS /RAS /CAS /WE DQM0 to DQM3 CKE CLK VDD VSS VDDQ VSSQ NC uc t

..

Ordering...