EDS2532JEBH-6B

EDS2532JEBH-6B is 256M bits SDRAM manufactured by Elpida Memory.

Features

- ×32 organization

- Single pulsed /RAS

- Burst read/write operation and burst read/single write operation capability

- Byte control by DQM

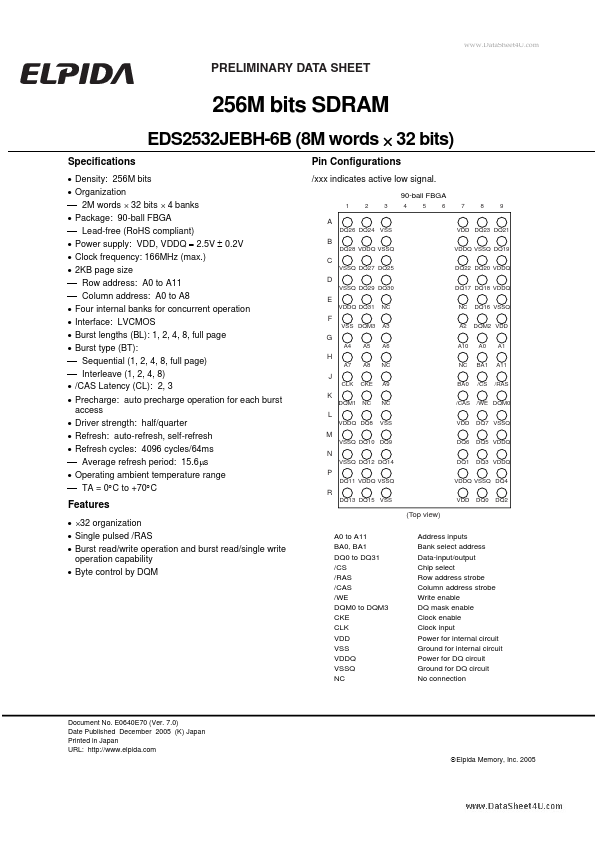

(Top view) A0 to A11 BA0, BA1 DQ0 to DQ31 /CS /RAS /CAS /WE DQM0 to DQM3 CKE CLK VDD VSS VDDQ VSSQ NC Address inputs Bank select address Data-input/output Chip select Row address strobe Column address strobe Write enable DQ mask enable Clock enable Clock input Power for internal circuit Ground for internal circuit Power for DQ circuit Ground for DQ circuit No connection

Document No. E0640E70 (Ver. 7.0) Date Published December 2005 (K) Japan Printed in Japan URL: http://.elpida. ©Elpida Memory, Inc. 2005

..

Ordering Information

Part number EDS2532JEBH-6B-E Supply voltage 2.5V Organization (words × bits) Internal Banks 8M × 32 4 Clock frequency MHz (max.) 166 /CAS latency 3 Package 90-ball FBGA

Part Number

E D S 25 32 J E BH

- 6B

- E

Elpida Memory Type

D: Monolithic Device

Environment Code E: Lead Free

Product Family S: SDRAM Density / Bank 25: 256M/4-bank, 4K Rows Organization 32: x32 Power Supply, Interface J: 2.5V, LVCMOS Die Rev. Package BH: FBGA(Board Type) Speed 6B: 166MHz/CL3

Preliminary Data Sheet E0640E70 (Ver. 7.0)

..

CONTENTS Specifications 1 Features

1 Pin Configurations...