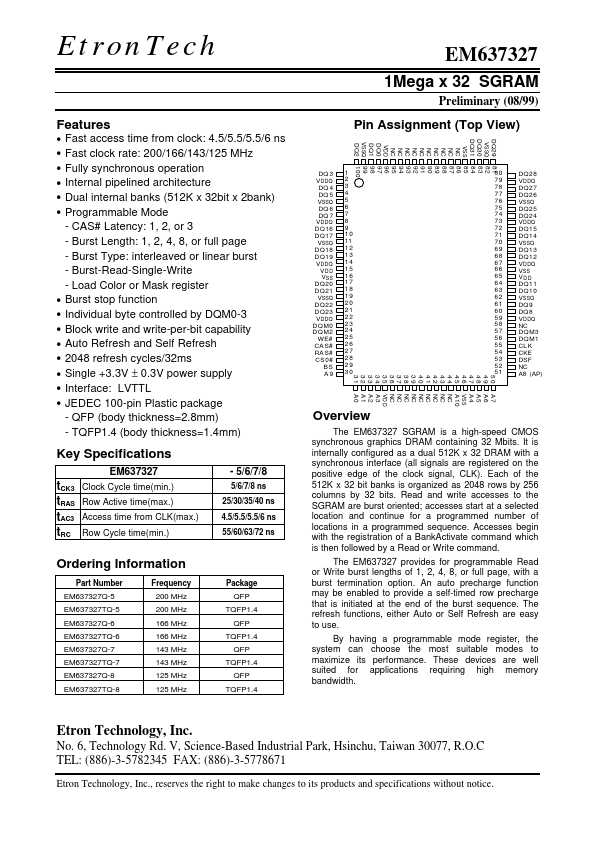

EM637327 Overview

Key Specifications

Package: QFP

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 3 V

Key Features

- CAS# Latency: 1, 2, or 3 - Burst Length: 1, 2, 4, 8, or full page

- Burst Type: interleaved or linear burst

- Burst-Read-Single-Write

- QFP (body thickness=2.8mm)