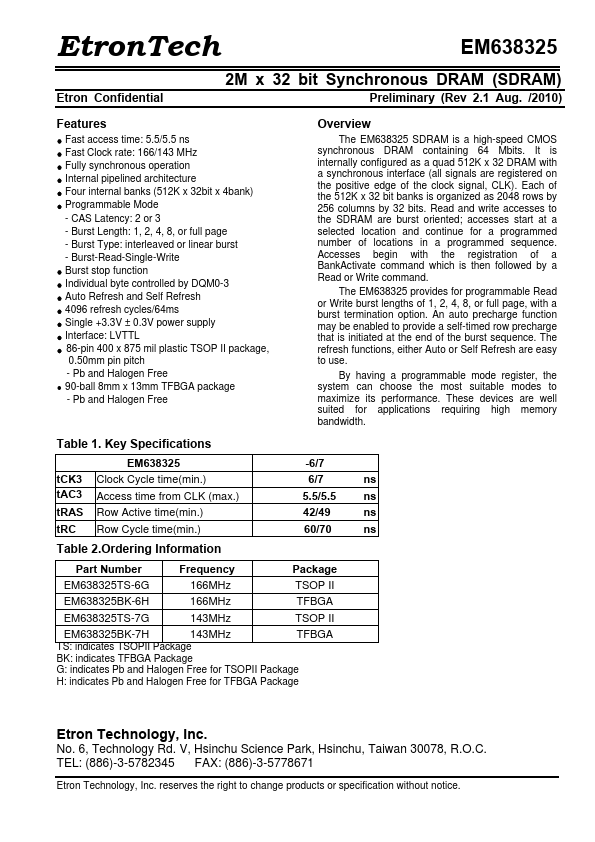

EM638325 Overview

Key Specifications

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 3 V

Length: 22.22 mm

Key Features

- Fast access time: 5.5/5.5 ns

- Fast Clock rate: 166/143 MHz

- Fully synchronous operation

- Internal pipelined architecture

- Four internal banks (512K x 32bit x 4bank)