XRT7300

XRT7300 is E3/DS3/STS-1 LINE INTERFACE UNIT manufactured by Exar.

DESCRIPTION

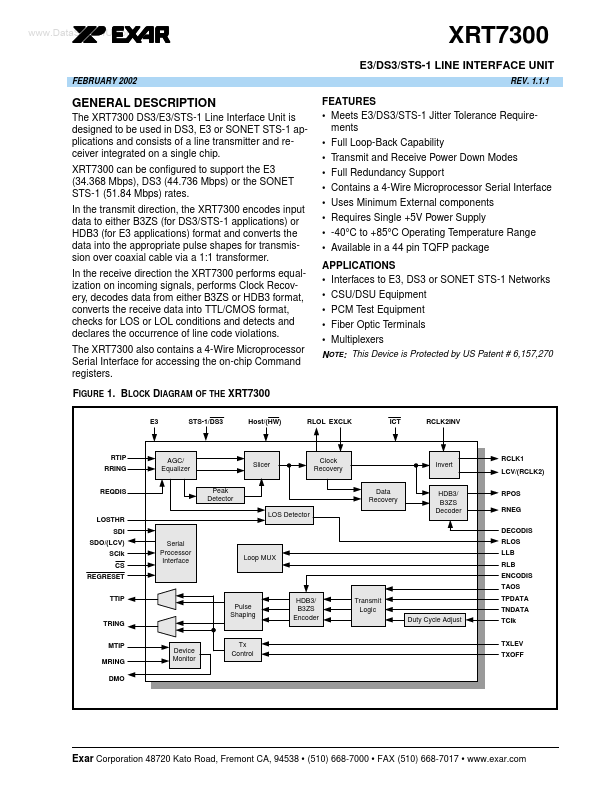

The XRT7300 DS3/E3/STS-1 Line Interface Unit is designed to be used in DS3, E3 or SONET STS-1 applications and consists of a line transmitter and receiver integrated on a single chip. XRT7300 can be configured to support the E3 (34.368 Mbps), DS3 (44.736 Mbps) or the SONET STS-1 (51.84 Mbps) rates. In the transmit direction, the XRT7300 encodes input data to either B3ZS (for DS3/STS-1 applications) or HDB3 (for E3 applications) format and converts the data into the appropriate pulse shapes for transmission over coaxial cable via a 1:1 transformer. In the receive direction the XRT7300 performs equalization on ining signals, performs Clock Recovery, decodes data from either B3ZS or HDB3 format, converts the receive data into TTL/CMOS format, checks for LOS or LOL conditions and detects and declares the occurrence of line code violations. The XRT7300 also contains a 4-Wire Microprocessor Serial Interface for accessing the on-chip mand registers. FIGURE 1. BLOCK DIAGRAM OF THE XRT7300

E3 STS-1/DS3 Host/(HW)

FEATURES

- Meets E3/DS3/STS-1 Jitter Tolerance Requirements

- Full Loop-Back Capability

- Transmit and Receive Power Down Modes

- Full Redundancy Support

- Contains a 4-Wire Microprocessor Serial Interface

- Uses Minimum External ponents

- Requires Single +5V Power Supply

- -40°C to +85°C Operating Temperature Range

- Available in a 44 pin TQFP package APPLICATIONS

- Interfaces to E3, DS3 or SONET STS-1 Networks

- CSU/DSU Equipment

- PCM Test Equipment

- Fiber Optic Terminals

- Multiplexers

NOTE: This Device is Protected by US Patent # 6,157,270

RLOL EXCLK

RCLK2INV

RTIP RRING REQDIS

AGC/ Equalizer Peak Detector

Slicer

Clock Recovery Data Recovery

Invert

RCLK1 LCV/(RCLK2)

LOSTHR SDI SDO/(LCV) SClk CS REGRESET TTIP Pulse Shaping TRING MTIP MRING DMO Tx Control Serial Processor Interface

LOS Detector

HDB3/ B3ZS Decoder

RPOS RNEG DECODIS RLOS LLB RLB ENCODIS TAOS TPDATA TNDATA

Loop MUX

HDB3/ B3ZS Encoder

Transmit Logic Duty Cycle...