XRT73L03

XRT73L03 is 3 CHANNEL E3/DS3/STS-1 LINE INTERFCE UNIT manufactured by Exar.

DESCRIPTION

The XRT73L03 is a 3-Channel, E3/DS3/STS-1 Line Interface Unit designed for E3, DS3 or SONET STS-1 applications and consists of three independent line transmitters and receivers integrated on a single chip. Each channel of the XRT73L03 can be configured to support the E3 (34.368 Mbps), DS3 (44.736 Mbps) or the SONET STS-1 (51.84 Mbps) rates. Each channel can be configured to operate in a mode/data rate that is independent of the other channels. In the transmit direction, each channel in the XRT73L03 encodes input data to either B3ZS or HDB3 format and converts the data into the appropriate pulse shapes for transmission over coaxial cable via a 1:1 transformer. In the receive direction, the XRT73L03 can perform Equalization on ining signals, perform Clock Recovery, decode data from either B3ZS or HDB3 format, convert the receive data into TTL/CMOS format, check for LOS or LOL conditions and detect and declare the occurrence of Line Code Violations. APPLICATIONS

- Digital Cross Connect Systems

- CSU/DSU Equipment

- Routers

- Fiber Optic Terminals

- Multiplexers

- ATM Switches FEATURES

- Meets E3/DS3/STS-1 Jitter Tolerance Requirements

- Full Loop-Back Capability

- Transmit and Receive Power Down Modes

- Full Redundancy Support

- Contains a 4-Wire Microprocessor Serial Interface

- Uses Minimum External ponents

- Single +3.3V Power Supply

- 5V tolerant I/O

- -40°C to +85°C Operating Temperature Range

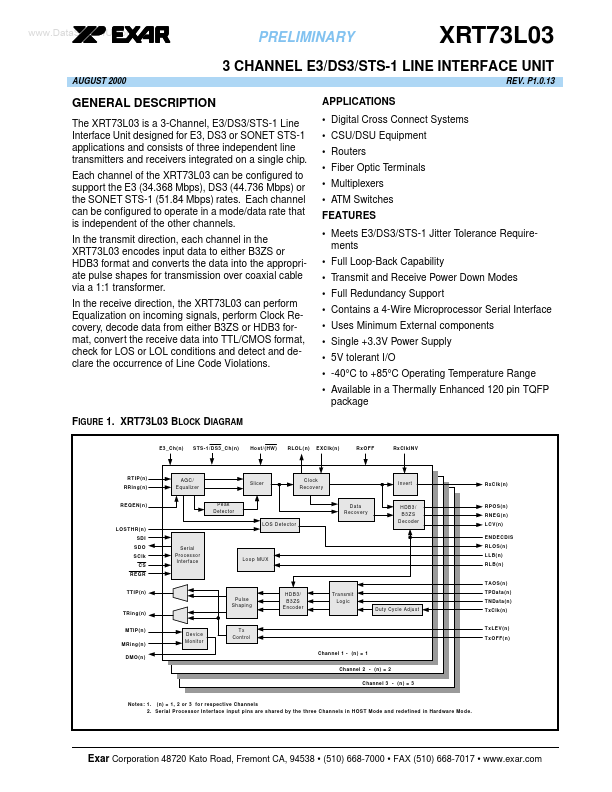

- Available in a Thermally Enhanced 120 pin TQFP package FIGURE 1. XRT73L03 BLOCK DIAGRAM

E3_Ch(n) STS-1/DS3_Ch(n) Host/(HW) RLOL(n) EXClk(n) Rx OFF Rx Clk INV

RTIP(n) RRing(n) REQEN(n)

AGC/ Equalizer Peak Detector

Slicer

Clock Recovery Data Recovery

Invert

Rx Clk(n)

LOSTHR(n) SDI SDO SClk CS REGR Serial Processor Interface

LOS Detector

HDB3/ B3ZS Decoder

RPOS(n) RNEG(n) LCV(n) ENDECDIS RLOS(n) LLB(n) RLB(n) TAOS(n)

Loop MUX

TTIP(n) Pulse Shaping TRing(n) MTIP(n) MRing(n) DMO(n) Tx Control

HDB3/ B3ZS Encoder

Transmit Logic Duty Cycle Adjust

TPData(n)...