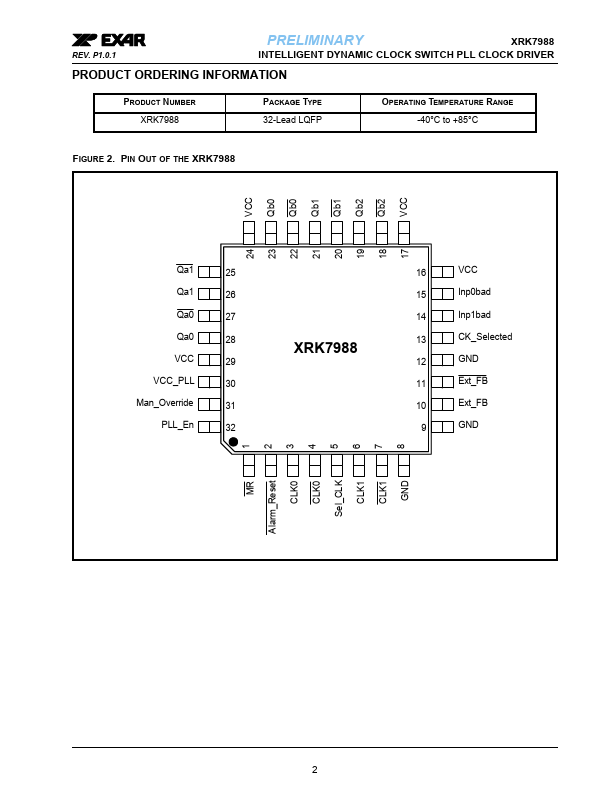

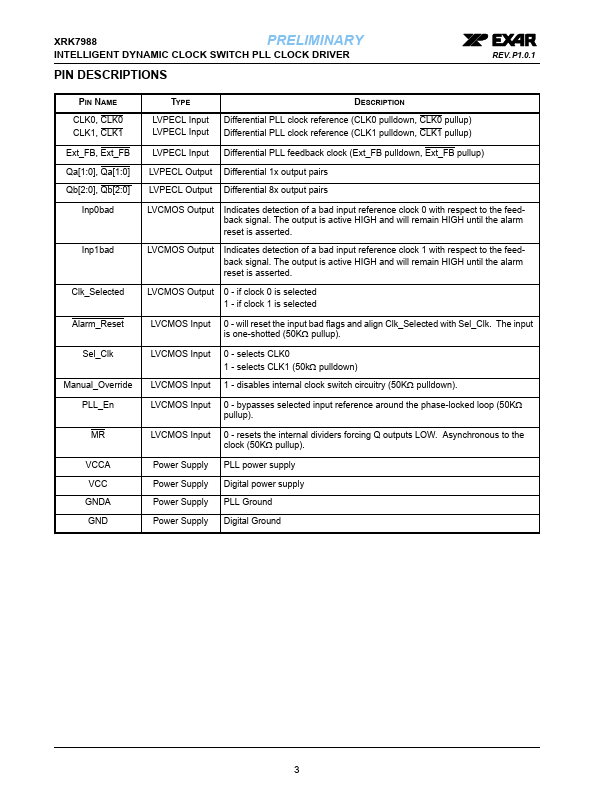

Datasheet Summary

.. xr

MARCH 2005

PRELIMINARY

REV. P1.0.1

INTELLIGENT DYNAMIC CLOCK SWITCH PLL CLOCK DRIVER device will switch to the good secondary clock and phase/frequency alignment will occur with minimal output phase disturbance. The typical phase bump caused by a failed clock is eliminated. Features

GENERAL DESCRIPTION

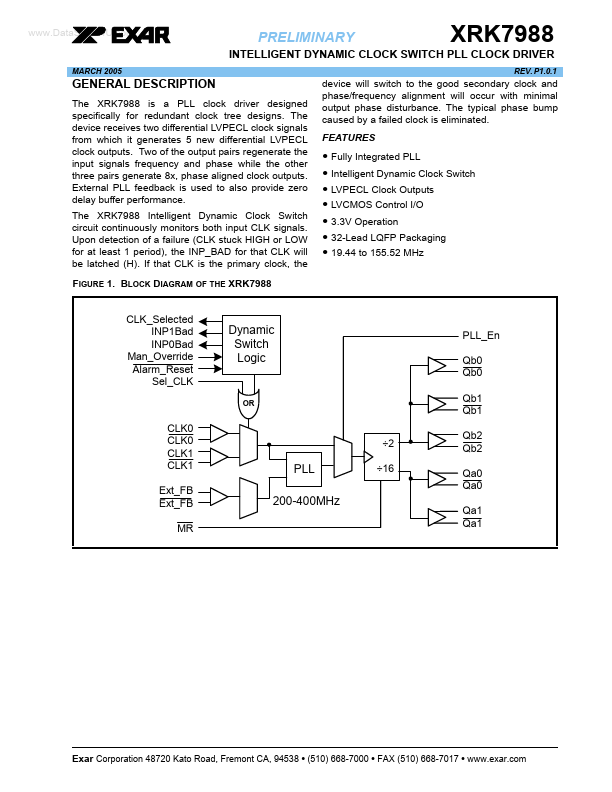

The XRK7988 is a PLL clock driver designed specifically for redundant clock tree designs. The device receives two differential LVPECL clock signals from which it generates 5 new differential LVPECL clock outputs. Two of the output pairs regenerate the input signals frequency and phase while the other three pairs generate 8x, phase aligned clock outputs....