74F403A

74F403A is First-In First-Out (FIFO) Buffer Memory manufactured by Fairchild Semiconductor.

- Part of the 74F comparator family.

- Part of the 74F comparator family.

Description

The 74F403A is an expandable fall-through type highspeed First-In First-Out (FIFO) Buffer Memory optimized for high-speed disk or tape controllers and munication buffer applications. It is organized as 16-words by 4-bits and may be expanded to any number of words or any number of bits in multiples of four. Data may be entered or extracted asynchronously in serial or parallel, allowing economical implementation of buffer memories. The 74F403A has 3-STATE outputs which provide added versatility and is fully patible with all TTL families.

Features s Serial or parallel input s Serial or parallel output s Expandable without external logic s 3-STATE outputs s Fully patible with all TTL families s Slim 24-pin package s 9403A replacement s Guaranteed 4000V minimum ESD protection

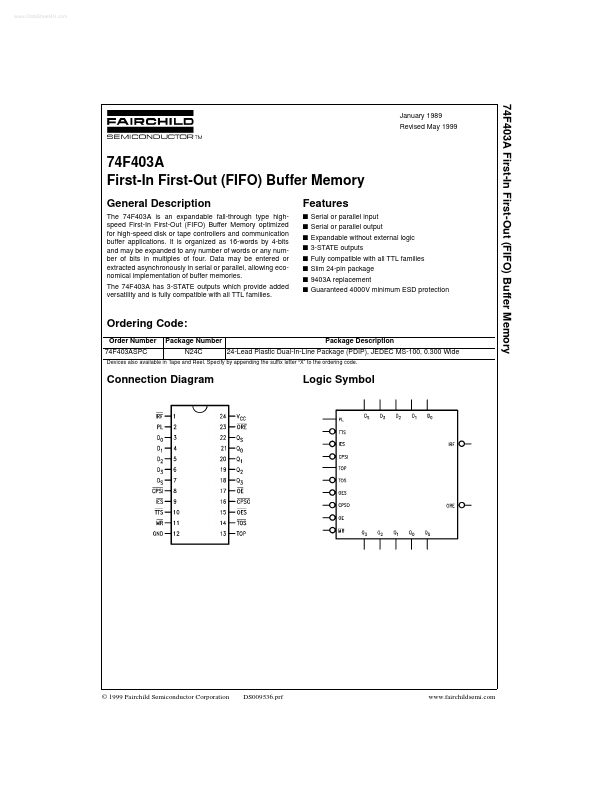

Ordering Code:

Order Number 74F403ASPC Package Number N24C Package Description

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Connection Diagram

Logic Symbol

© 1999 Fairchild Semiconductor Corporation

DS009536.prf

.fairchildsemi.

Unit Loading/Fan Out:

See Section 2 for U.L. definitions

Pin Description

Names D0

- D3 Parallel Data Inputs DS PL CPSI IES TTS OES TOS TOP MR OE CPSO Serial Data Input Parallel Load Input Serial Input Clock Serial Input Enable Transfer to Stack Input Serial Output Enable Transfer Out Serial Transfer Out Parallel Master Reset Output Enable Serial Output Clock HIGH/LOW Output IOH/IOL 1.0/0.667 1.0/0.667 1.0/0.667 1.0/0.667 1.0/0.667 1.0/0.667 1.0/0.667 1.0/0.667 1.0/0.667 1.0/0.667 1.0/0.667 1.0/0.667 285/26.7 285/26.7 20/13.3 20/13.3 20 µA/400 µA 20 µA/400 µA 20 µA/400 µA 20 µA/400 µA 20 µA/400 µA 20 µA/400 µA 20 µA/400 µA 20 µA/400 µA 20 µA/400 µA 20 µA/400 µA 20 µA/400 µA 20 µA/400 µA 5.7 m A/16 m A 5.7 m A/16 m A U.L. Input IIH/IIL

Block Diagram

Q0

- Q3 Parallel Data Outputs QS IRF ORE Serial Data Output Input...