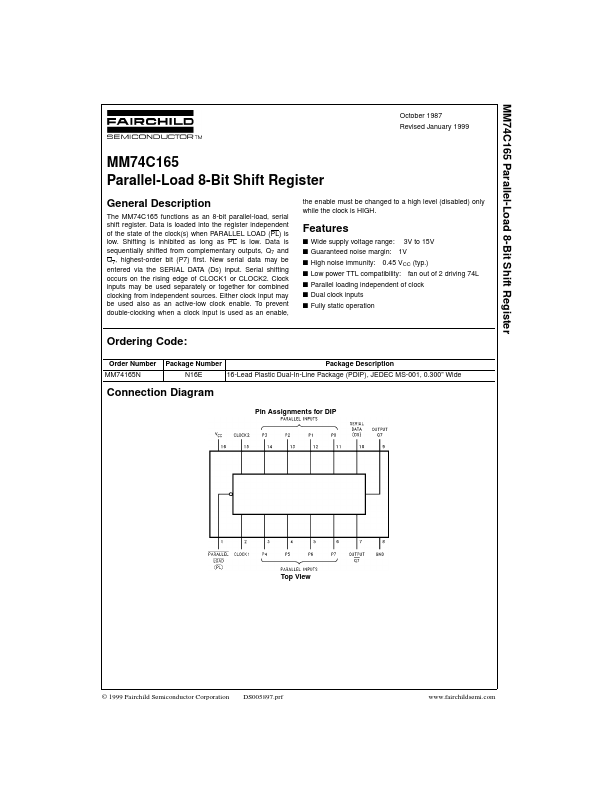

| Part | MM74165N |

|---|---|

| Description | Parallel-Load 8-Bit Shift Register |

| Manufacturer | Fairchild Semiconductor |

| Size | 50.96 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 74HC595 | onsemi | 8-Bit Serial-Input/Serial or Parallel-Output Shift Register |

| MPU6050 | InvenSense | Register Map and Descriptions |

| HD74LS194AP | Renesas | 4-bit Bidirectional Universal Shift Register |