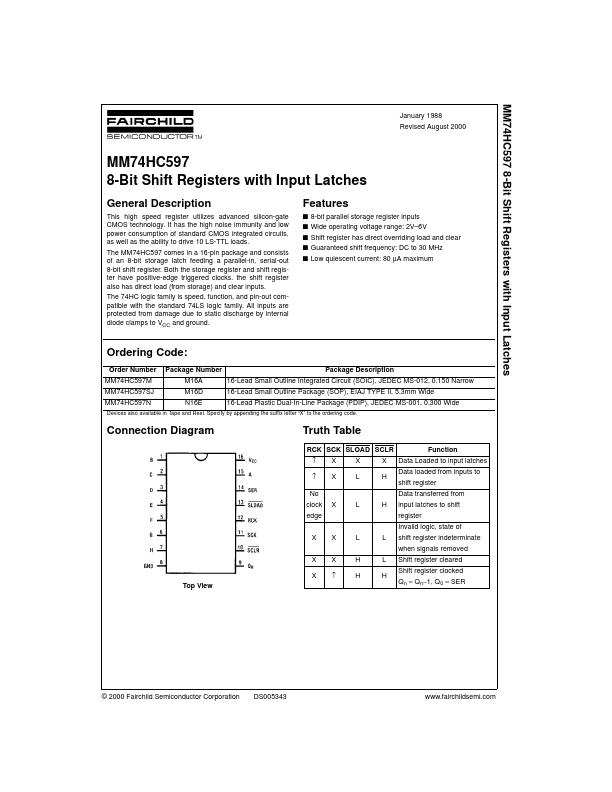

MM74HC597 Overview

Description

This high speed register utilizes advanced silicon-gate CMOS technology. It has the high noise immunity and low power consumption of standard CMOS integrated circuits, as well as the ability to drive 10 LS-TTL loads.

Key Features

- Specify by appending the suffix letter “X” to the ordering code