MD7IC21100NR1

Key Features

- 100% PAR Tested for Guaranteed Output Power Capability

- On - Chip Matching (50 Ohm Input, on a per side basis, DC Blocked)

- Internally Matched for Ease of Use

- Integrated Quiescent Current Temperature pensation with Enable/ Disable Function (1)

- Integrated ESD Protection

- 225°C Capable Plastic Package

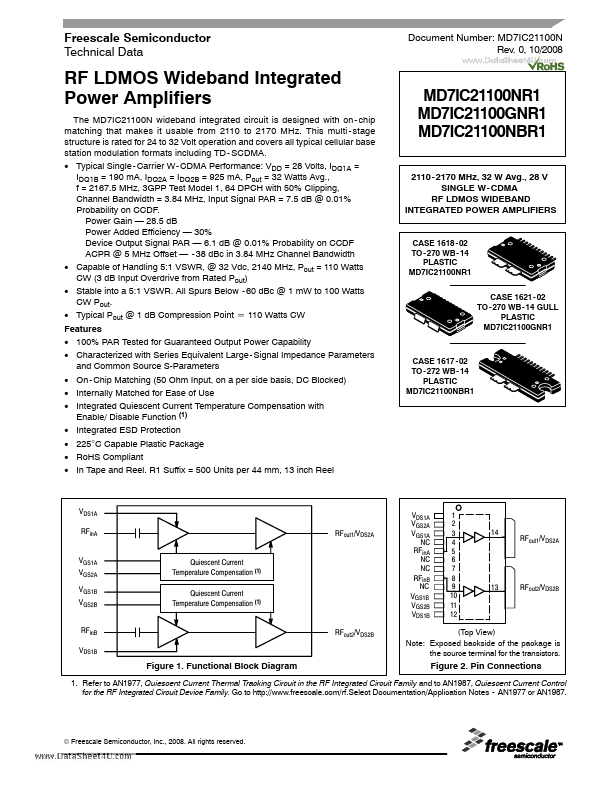

- Functional Figure

- Characteristic Table

- Moisture Sensitivity Level Test Methodology Per JESD22 - A113, IPC/JEDEC J - STD - 020 Rating 3 Package Peak Temperature 260 Unit °C Table

- Characteristic Stage 1 - Off Characteristics (4) Symbol IDSS IDSS IGSS Min - - - Typ - - - Max 10 1 1 Unit μAdc μAdc