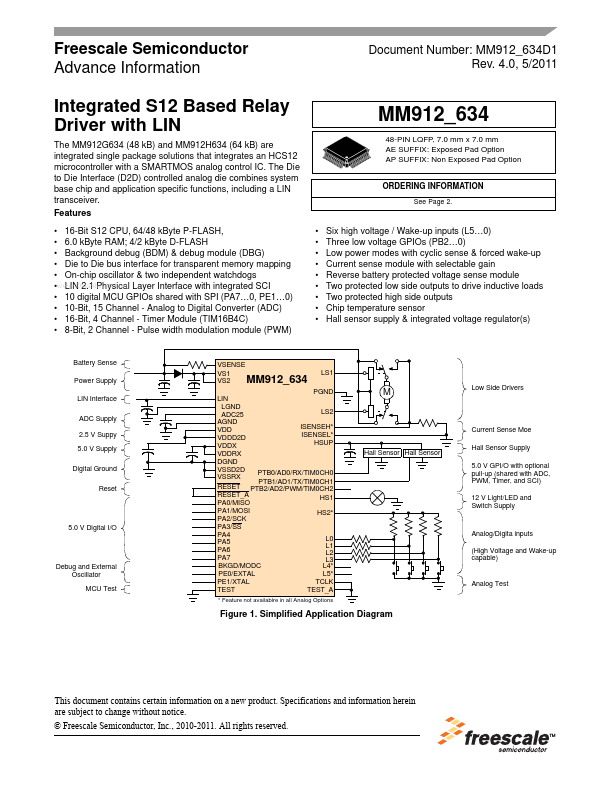

MM912H634CM1AE Overview

Key Features

- 6.0 kByte RAM; 4/2 kByte D-FLASH

- Background debug (BDM) & debug module (DBG)

- Die to Die bus interface for transparent memory mapping

- On-chip oscillator & two independent watchdogs

- LIN 2.1 Physical Layer Interface with integrated SCI

- 10-Bit, 15 Channel

- Analog to Digital Converter (ADC)

- 16-Bit, 4 Channel

- Timer Module (TIM16B4C)

- 8-Bit, 2 Channel