MBM29LV001TC Key Features

- Single 3.0 V read, program, and erase Minimizes system level power requirements

- patible with JEDEC-standard mands Uses same software mands as E2PROMs

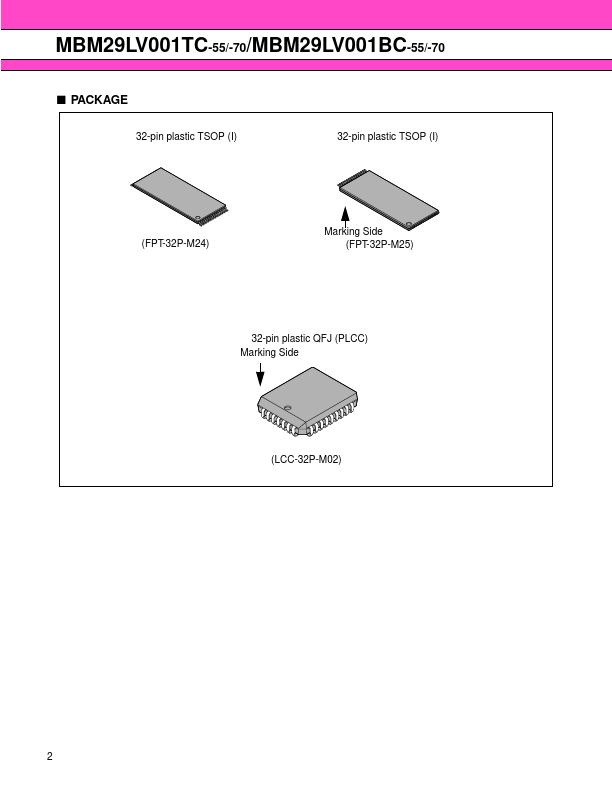

- patible with JEDEC-standard world-wide pinouts 32-pin TSOP(I) (Package suffix: PFTN

- Normal Bend Type, PFTR

- Reversed Bend Type) 32-pin PLCC (Package suffix: PD)

- Minimum 100,000 program/erase cycles

- High performance 55 ns maximum access time

- Sector erase architecture One 8K byte, two 4K bytes, and seven 16K bytes Any bination of sectors can be concurrently era

- Boot Code Sector Architecture T = Top sector B = Bottom sector

- Embedded EraseTM Algorithms Automatically pre-programs and erases the chip or any sector