MB8264-15

MB8264-15 is NMOS Dynamic Random Access Memory manufactured by Fujitsu Semiconductor Limited.

DESCRIPTION

The Fujitsu MB8264 is a fully decoded, dynamic NMOS random access memory organized as 65536 one-bit words. The design Is optimized for high-speed, high performance applications such as mainframe memory, buffer memory, peripheral storage and environments where low power dissipation and pact layout are required.

Multiplexed row and column address inputs permit the MB8264 to be housed In a standard 16-pln DIP. Pln-outs conform to the JEDEC approved pin out.

The MB8264 is fabricated using silicon-gate NMOS and Fujitsu's advanced Double-Layer Polysilicon process. This process, coupled with single-transistor memory storage cells, permits maximum circuit density and minimal chip size. Dynamic Circuitry Is employed in the design, including the sense amplifiers.

Clock timing requirements are noncritical, and power supply tolerance is :!: 10%. All inputs/outputs are TTL patible.

FEATURES

.65,536 x 1 RAM,16-pln package

- Sillcon-gate, Double Poly NMOS, single transistor cell

- Row access time: 150ns Max (MB8264-15) 200ns Max (MB8264-20)

- Cycle time: 270ns Min (MB8264-15) 330ns Min (MB8264-20)

- Low power: 22 m W Max Standby 275 m W Max Active (MB8264-15) 248 m W Max Active (MB8264-20)

- :!:10% tolerance on +5V Supply

- On-chlp substrate bias generator

- All Inputs TTL patible, low capacitive load

- Three-state TTL patible output

- "Gated" CAS .128 refresh cycles

- mon 110 capability using "Early Write" operation

- Output unlatched at cycle end allows extended page boundary and twodimensional chip select

- Read-Modlfy-Wrlte, RASonly refresh, and Page-Mode capability

- On-chlp latches for Addresses and Date- ln

- Hidden Refresh Capability

- Pin patible with HM4864, MK4164, TMS4164, MCM8665, JL PD4164 and IMS2600

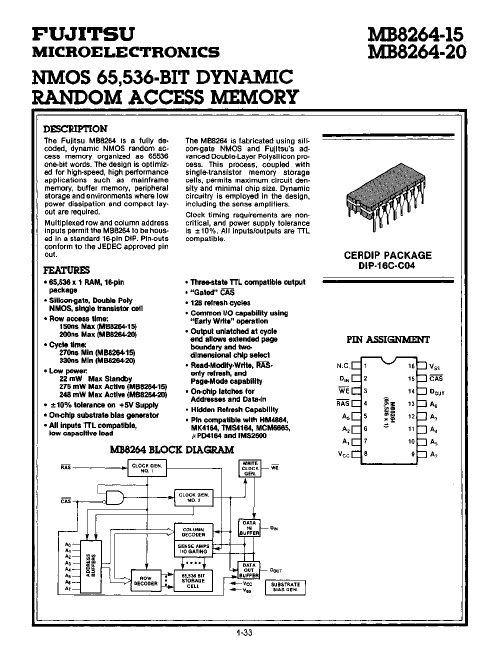

:MB8264 BLOCK DIAGRAM li As -------io-

MB8264- 15 MB8264- 20

CERDIP PACKAGE DIP- 16C- C04

PIN ASSIGNMENT

N.C.

D'N

WE 3

RAs 4 ~I:

Ao 5 ;i5:

A2 6

A, 7

Vee 8

Vss CAS

DOUT

A6 A3 A4 As A7

1- 33

YB8264-15/YB8264-2...