GS8170DD36C-333

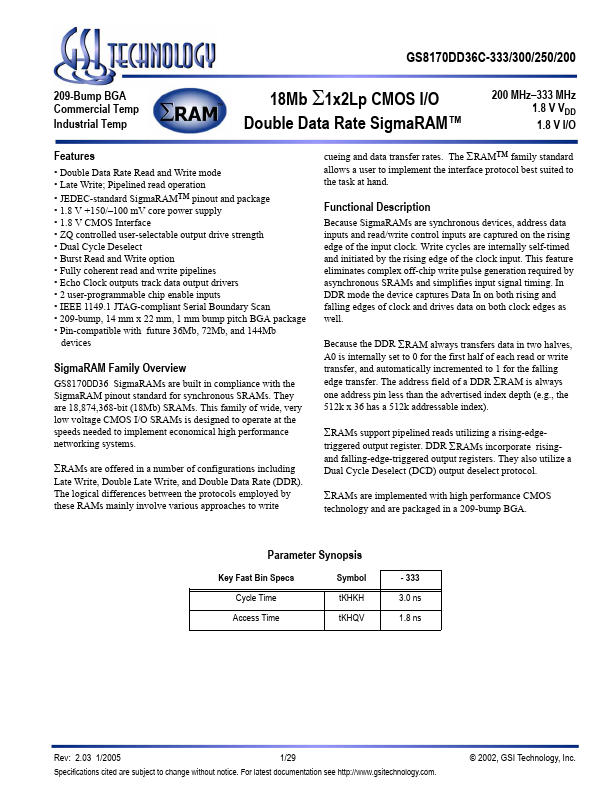

GS8170DD36C-333 is Double Data Rate SigmaRAM manufactured by GSI Technology.

- Part of the GS8170DD36C comparator family.

- Part of the GS8170DD36C comparator family.

GS8170DD36C-333/300/250/200

209-Bump BGA mercial Temp Industrial Temp Features

- Double Data Rate Read and Write mode

- Late Write; Pipelined read operation

- JEDEC-standard Sigma RAM™ pinout and package

- 1.8 V +150/- 100 m V core power supply

- 1.8 V CMOS Interface

- ZQ controlled user-selectable output drive strength

- Dual Cycle Deselect

- Burst Read and Write option

- Fully coherent read and write pipelines

- Echo Clock outputs track data output drivers

- 2 user-programmable chip enable inputs

- IEEE 1149.1 JTAG-pliant Serial Boundary Scan

- 209-bump, 14 mm x 22 mm, 1 mm bump pitch BGA package

- Pin-patible with future 36Mb, 72Mb, and 144Mb devices

18Mb Σ1x2Lp CMOS I/O Double Data Rate Sigma RAM™

200 MHz- 333 MHz 1.8 V VDD 1.8 V I/O cueing and data transfer rates. The ΣRAM™ family standard allows a user to implement the interface protocol best suited to the task at hand.

Functional Description

Because Sigma RAMs are synchronous devices, address data inputs and read/write control inputs are captured on the rising edge of the input clock. Write cycles are internally self-timed and initiated by the rising edge of the clock input. This feature eliminates plex off-chip write pulse generation required by asynchronous SRAMs and simplifies input signal timing. In DDR mode the device captures Data In on both rising and falling edges of clock and drives data on both clock edges as well. Because the DDR ΣRAM always transfers data in two halves, A0 is internally set to 0 for the first half of each read or write transfer, and automatically incremented to 1 for the falling edge transfer. The address field of a DDR ΣRAM is always one address pin less than the advertised index depth (e.g., the 512k x 36 has a 512k addressable index).

Sigma RAM Family Overview

GS8170DD36 Sigma RAMs are built in pliance with the Sigma RAM pinout standard for synchronous SRAMs. They are 18,874,368-bit (18Mb) SRAMs. This family of wide, very low voltage CMOS I/O SRAMs is designed to...