GS8330DW72

GS8330DW72 is 36M Double Late Write SRAM manufactured by GSI Technology.

- Part of the GS8330DW36 comparator family.

- Part of the GS8330DW36 comparator family.

Preliminary GS8330DW36/72C-250/200

209-Bump BGA mercial Temp Industrial Temp

36Mb Σ1x1Dp CMOS I/O

Double Late Write Sigma RAM™

200 MHz- 250 MHz 1.8 V VDD 1.8 V I/O

Features

- Double Late Write mode, Pipelined Read mode

- JEDEC-standard Sigma RAM™ pinout and package

- 1.8 V +150/- 100 m V core power supply

- 1.8 V CMOS Interface

- ZQ controlled user-selectable output drive strength

- Dual Cycle Deselect

- Burst Read and Write option

- Fully coherent read and write pipelines

- Echo Clock outputs track data output drivers

- Byte write operation (9-bit bytes)

- 2 user-programmable chip enable inputs

- IEEE 1149.1 JTAG-pliant Serial Boundary Scan

- 209-bump, 14 mm x 22 mm, 1 mm bump pitch BGA package

- Pin-patible with future 72Mb and 144Mb devices Key Fast Bin Specs Cycle Time Access Time Symbol t KHKH t KHQV -250 4.0 ns 2.1 ns

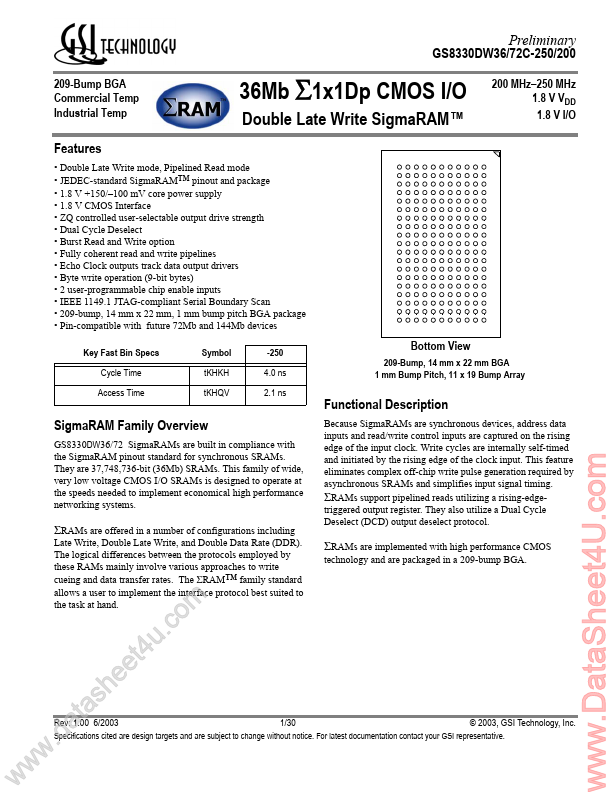

Bottom View

209-Bump, 14 mm x 22 mm BGA 1 mm Bump Pitch, 11 x 19 Bump Array

Functional Description

Because Sigma RAMs are synchronous devices, address data inputs and read/write control inputs are captured on the rising edge of the input clock. Write cycles are internally self-timed and initiated by the rising edge of the clock input. This feature eliminates plex off-chip write pulse generation required by asynchronous SRAMs and simplifies input signal timing. ΣRAMs support pipelined reads utilizing a rising-edgetriggered output register. They also utilize a Dual Cycle Deselect (DCD) output deselect protocol.

Sigma RAM Family Overview

GS8330DW36/72 Sigma RAMs are built in pliance with the Sigma RAM pinout standard for synchronous SRAMs. They are 37,748,736-bit (36Mb) SRAMs. This family of wide, very low voltage CMOS I/O SRAMs is designed to operate at the speeds needed to implement economical high performance networking systems.

ΣRAMs are offered in a number of configurations including

Late Write, Double Late Write, and Double Data Rate (DDR). The logical differences between the protocols employed by these RAMs mainly involve various...