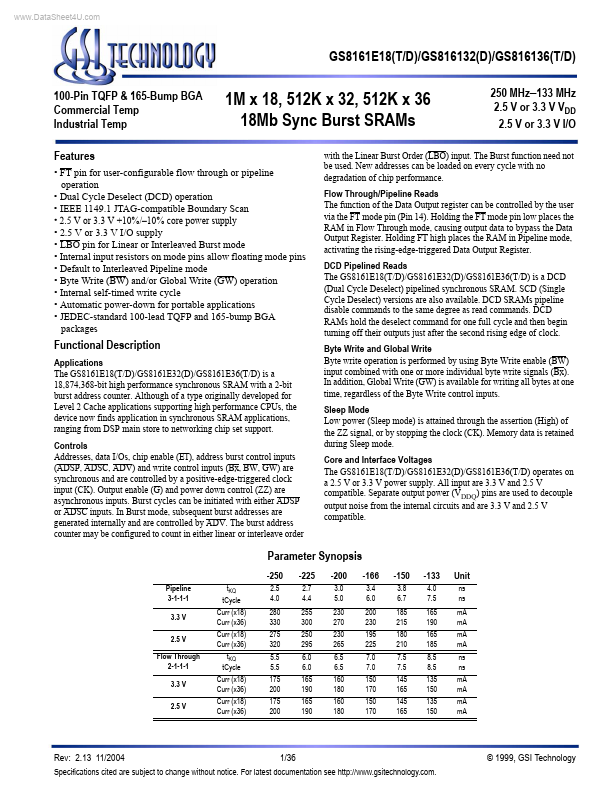

GS8161E18

Features

- FT pin for user-configurable flow through or pipeline operation

- Dual Cycle Deselect (DCD) operation

- IEEE 1149.1 JTAG-patible Boundary Scan

- 2.5 V or 3.3 V +10%/- 10% core power supply

- 2.5 V or 3.3 V I/O supply

- LBO pin for Linear or Interleaved Burst mode

- Internal input resistors on mode pins allow floating mode pins

- Default to Interleaved Pipeline mode

- Byte Write (BW) and/or Global Write (GW) operation

- Internal self-timed write cycle

- Automatic power-down for portable applications

- JEDEC-standard 100-lead TQFP and 165-bump BGA packages

1M x 18, 512K x 32, 512K x 36 18Mb Sync Burst SRAMs

250 MHz- 133 MHz 2.5 V or 3.3 V VDD 2.5 V or 3.3 V I/O with the Linear Burst Order (LBO) input. The Burst function need not be used. New addresses can be loaded on every cycle with no degradation of chip performance.

Flow Through/Pipeline Reads

The function of the Data Output register can be controlled by the user via the FT mode pin (Pin 14). Holding the FT mode pin low...