HD74HC76

Description

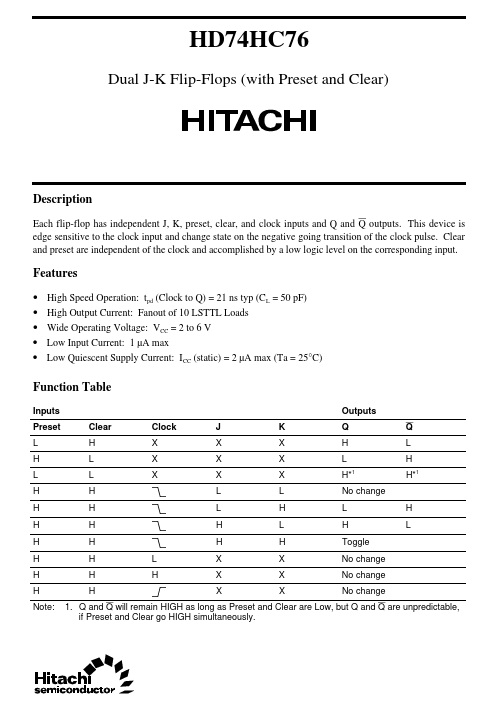

Each flip-flop has independent J, K, preset, clear, and clock inputs and Q and Q outputs. This device is edge sensitive to the clock input and change state on the negative going transition of the clock pulse. Clear and preset are independent of the clock and acplished by a low logic level on the corresponding input.

Features

- -

- -

- High Speed Operation: tpd (Clock to Q) = 21 ns typ (CL = 50 p F) High Output Current: Fanout of 10 LSTTL Loads Wide Operating Voltage: VCC = 2 to 6 V Low Input Current: 1 µA max Low Quiescent Supply Current: ICC (static) = 2 µA max (Ta = 25°C)

Function Table

Inputs Preset L H L H H H H H H H Note: Clear H L L H H H H H H H L H Clock X X X J X X X L L H H X X X K X X X L H L H X X X Outputs Q H L H-

Q L H H- 1

No change L H Toggle No change No change No change H L

1. Q and Q will remain HIGH as long as Preset and Clear are Low, but Q and Q are unpredictable, if Preset and Clear go HIGH simultaneously.

Pin Arrangement

1CK 1 1PR...