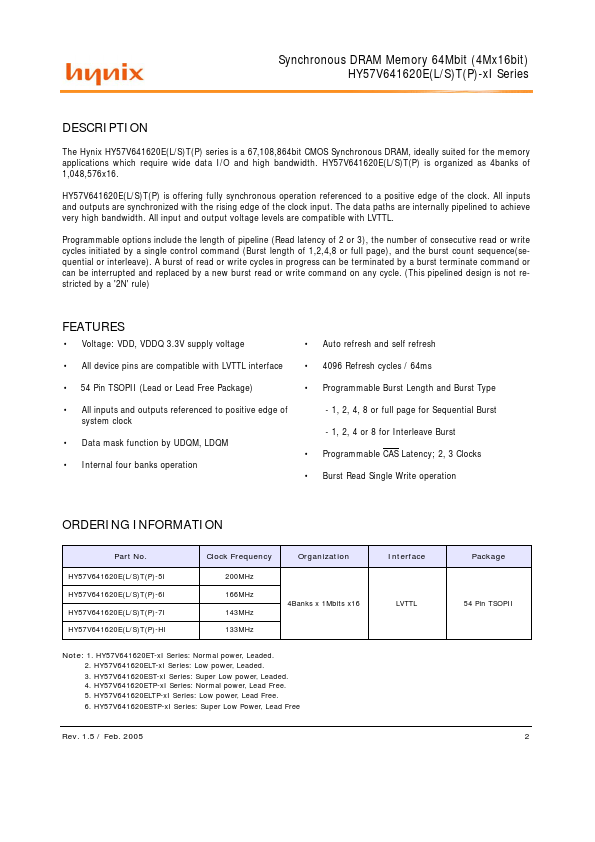

Datasheet Summary

m o c . 64Mb Synchronous DRAM based on 1M x 4Bank x16 I/O U 4 t e e Document Title h S a Revision at History .D w w w

4Bank x 1M x 16bits Synchronous DRAM

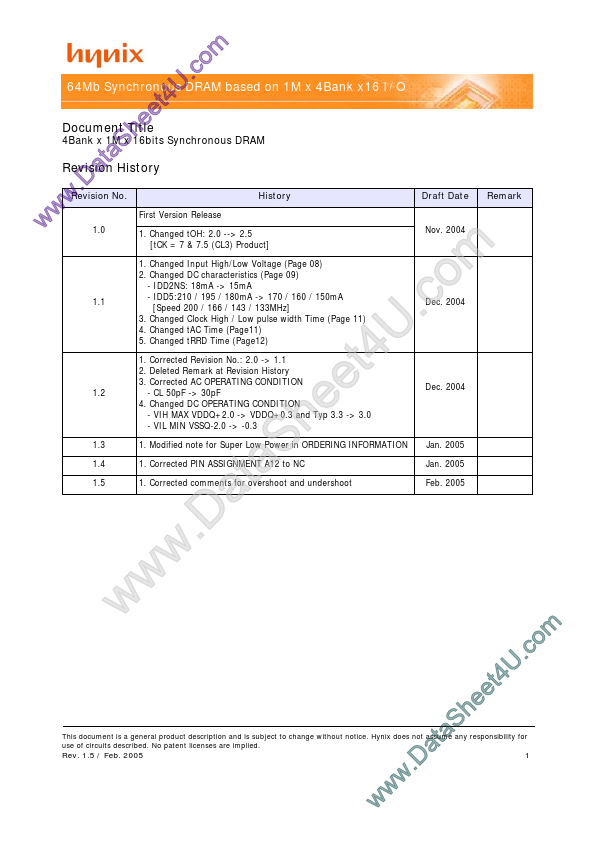

Revision No. History First Version Release 1.0 1. Changed tOH: 2.0 --> 2.5 [tCK = 7 & 7.5 (CL3) Product] 1.1 1. Changed Input High/Low Voltage (Page 08) 2. Changed DC characteristics (Page 09)

- IDD2NS: 18mA -> 15mA

- IDD5:210 / 195 / 180mA -> 170 / 160 / 150mA [Speed 200 / 166 / 143 / 133MHz] 3. Changed Clock High / Low pulse width Time (Page 11) 4. Changed tAC Time (Page11) 5. Changed tRRD Time (Page12)

Draft Date

Remark

Nov. 2004

1.3 1.4 1.5 m o .c U 4 t e e h S a t a .D w w w

Dec. 2004 1. Corrected Revision No.: 2.0 -> 1.1...