HY5S6B6

description and is subject to change without notice. Hynix does not assume any responsibility for use of circuits described. No patent licenses are implied. Rev 0.3 / July 2004 1 w w w

.D at h S a t e e

4U

. m o c

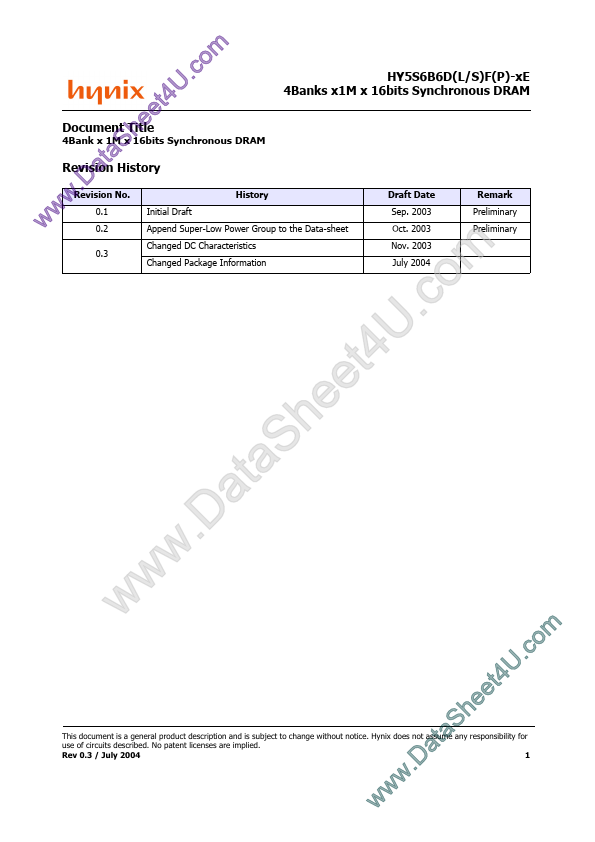

HY5S6B6D(L/S)F(P)-x E 4Banks x1M x 16bits Synchronous DRAM

DESCRIPTION

The Hynix Low Power SDRAM is suited for non-PC application which use the batteries such as PDAs, 2.5G and 3G cellular phones with internet access and multimedia capabilities, mini-notebook, handheld PCs. The Hynix HY5S6B6D(L/S)F(P) is a 67,108,864bit CMOS Synchronous Dynamic Random Access Memory. It is organized as 4banks of 1,048,576x16. The Low Power SDRAM provides for programmable options including CAS latency of 1, 2, or 3, READ or WRITE burst length of 1, 2, 4, 8, or full page, and the burst count sequence(sequential or interleave). And the Low Power SDRAM also provides for special programmable options including Partial Array Self Refresh of a quarter bank, a half bank, 1bank, 2banks, or...