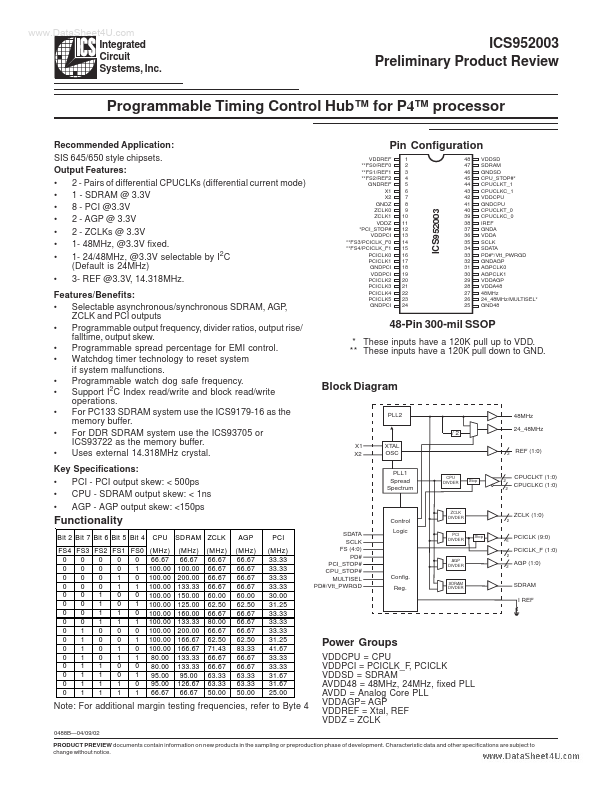

ICS952003 Key Features

- Pairs of differential CPUCLKs (differential current mode)

- SDRAM @ 3.3V

- PCI @3.3V

- AGP @ 3.3V

- ZCLKs @ 3.3V

- 1- 48MHz, @3.3V fixed

- 1- 24/48MHz, @3.3V selectable by I2C (Default is 24MHz)

- 3- REF @3.3V, 14.318MHz. Features/Benefits

- Selectable asynchronous/synchronous SDRAM, AGP, ZCLK and PCI outputs

- Programmable output frequency, divider ratios, output rise/ falltime, output skew