ICS554-01A

ICS554-01A is LOW SKEW 1 TO 4 CLOCK BUFFER manufactured by ICST.

..

LOW SKEW 1 TO 4 CLOCK BUFFER PECL IN, PECL OUT

Description

The ICS554-01A is a low skew clock buffer with a single plimentary PECL input to four PECL outputs. Part of ICS’ Clock Blocks TM family, this is our lowest skew PECL clock buffer. The ICS554-01A is footprint patible with the ICS554-01, but requires fewer passive ponents for termination thus providing a cost-saving alternative. For parts which do not require PECL inputs or outputs, see the ICS553 for a 1 to 4 low skew buffer, or the ICS552-02 for a 1 to 8 low skew buffer. For more than 8 outputs see the MK74CBxxx Buffalo TM series of clock drivers. ICS makes many non-PLL and PLL based low skew output devices as well as Zero Delay Buffers to synchronize clocks. Contact us for all of your clocking needs.

Features

- -

- -

- -

- -

- Input frequency up to 200 MHz Advanced CMOS process Outputs are skew matched to within 50 ps Packaged in 16-pin TSSOP One PECL input to 4 PECL output clock drivers Operating Voltages of 3.3 V or 5 V Industrial temperature range Functional equivalent to ICS554-01 Simplified passive termination network pared to ICS554-01

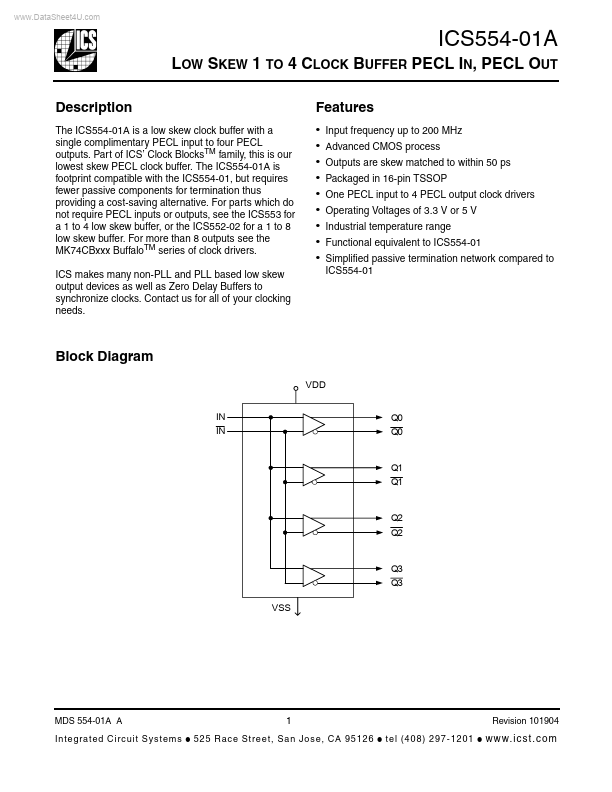

Block Diagram

VDD IN IN Q0 Q0

Q1 Q1

Q2 Q2

Q3 Q3 VSS

MDS 554-01A A I n t e gra te d C i r c u i t S y s t e m s

- 1

525 Race Stre et, San Jo se, CA 9 5126

- Revision 101904 te l (40 8) 2 97-12 01

- w w w. i c st . c o m

ICS554-01A LOW SKEW 1 TO 4 CLOCK BUFFER PECL IN, PECL OUT

Pin Assignment

NC VDD Q0 Q0 Q1 Q1 GND IN 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 NC VDD Q3 Q3 Q2 Q2 GND IN

16-pin 173 mil (0.65mm) TSSOP

Pin Descriptions

Number

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Name

NC VDD Q0 Q0 Q1 Q1 GND IN IN GND Q2 Q2 Q3 Q3 VDD...