ICS558-01

ICS558-01 is PECL/CMOS TO CMOS CLOCK DIVIDER manufactured by ICST.

..

PECL/CMOS TO CMOS CLOCK DIVIDER

Description

The ICS558-01 accepts a high speed input of either PECL or CMOS, integrates a divider of 1, 2, 3, or 4, and provides four CMOS low skew outputs. The chip also has output enables so that one, three, or all four outputs can be tri-stated. The ICS558-01 is a member of the ICS Clock Blocks™ family of clock generation, synchronization, and distribution devices.

Features

- -

- -

- -

- -

- -

16-pin TSSOP package Available in Pb (lead) free package Selectable PECL or CMOS inputs Operates up to 250 MHz Works as a voltage translator Four low skew (<250 ps) outputs Selectable internal divider Operating input voltages of 3.3 V or 5.0 V Operating output voltages of 2.5 V, 3.3 V or 5.0 V Ideal for IA64 designs

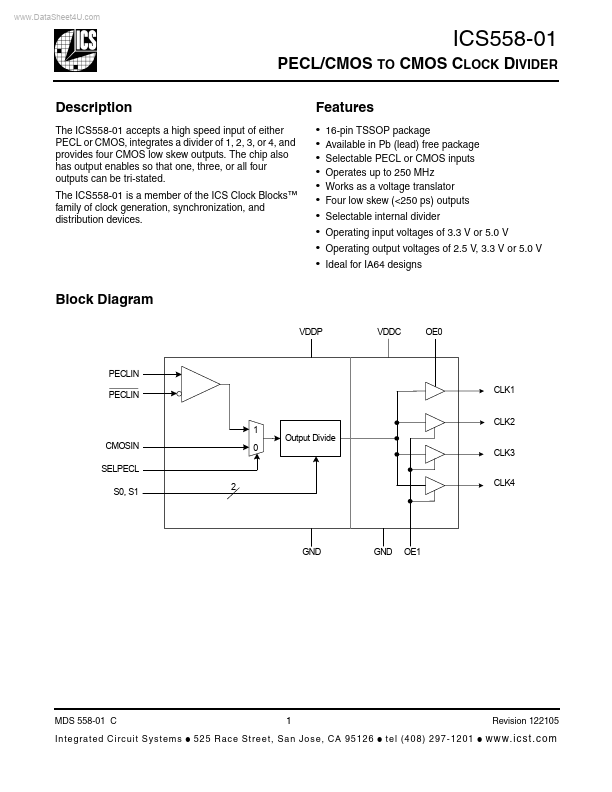

Block Diagram

VDDP VDDC OE0

PECLIN PECLIN CLK1 CLK2 Output Divide CLK3 CLK4

1 CMOSIN SELPECL S0, S1 2 0

OE1

MDS 558-01 C I n t e gra te d C i r c u i t S y s t e m s

- 1

525 Race Stre et, San Jo se, CA 9 5126

- Revision 122105 te l (40 8) 2 97-12 01

- w w w. i c st . c o m

ICS558-01 PECL/CMOS TO CMOS CLOCK DIVIDER

Pin Assignment

S0 S1 VDDP PECLIN PECLIN GND CMOSIN OE0 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 SELPECL VDDC CLK1 CLK2 CLK3 CLK4 GND OE1

Input Clock Selection

SELPECL 0 1 Input CMOSIN PECLIN

Tri-State Table

OE1 0 0 1 1 OE0 0 1 0 1 CLK 1 Tri-state Clock ON Tri-state Clock ON CLK 2, 3, 4 Tri-state Tri-state Clock ON Clock ON

16-pin 173 Mil (0.65mm) TSSOP

Output Divide...