ICS8535-01

ICS8535-01 is LVPECL FANOUT BUFFER manufactured by ICST.

..

Integrated Circuit Systems, Inc.

LOW SKEW, 1-TO-4 LVCMOS-TO-3.3V LVPECL FANOUT BUFFER

Features

- 4 differential 3.3V LVPECL outputs

- Selectable CLK0 or CLK1 inputs for redundant and multiple frequency fanout applications

- CLK0 or CLK1 can accept the following differential input levels: LVCMOS or LVTTL

- Maximum output frequency up to 266MHz

- Translates LVCMOS and LVTTL levels to 3.3V LVPECL levels

- Output skew: 30ps (maximum)

- Part-to-part skew: 150ps (maximum)

- Propagation delay: 1.9ns (maximum)

- 3.3V operating supply

- 0°C to 70°C ambient operating temperature

- Industrial temperature information available upon request

GENERAL DESCRIPTION

The ICS8535-01 is a low skew, high performance 1-to-4 LVCMOS-to-3.3V LVPECL fanout buffer Hi Per Clock S™ and a member of the Hi Per Clock S™ family of High Performance Clock Solutions from ICS. The ICS8535-01 has two single ended clock inputs. the single ended clock input accepts LVCMOS or LVTTL input levels and translate them to 3.3V LVPECL levels. The clock enable is internally synchronized to eliminate runt clock pulses on the output during asynchronous assertion/ deassertion of the clock enable pin.

,&6

Guaranteed output and part-to-part skew characteristics make the ICS8535-01 ideal for those applications demanding well defined performance and repeatability.

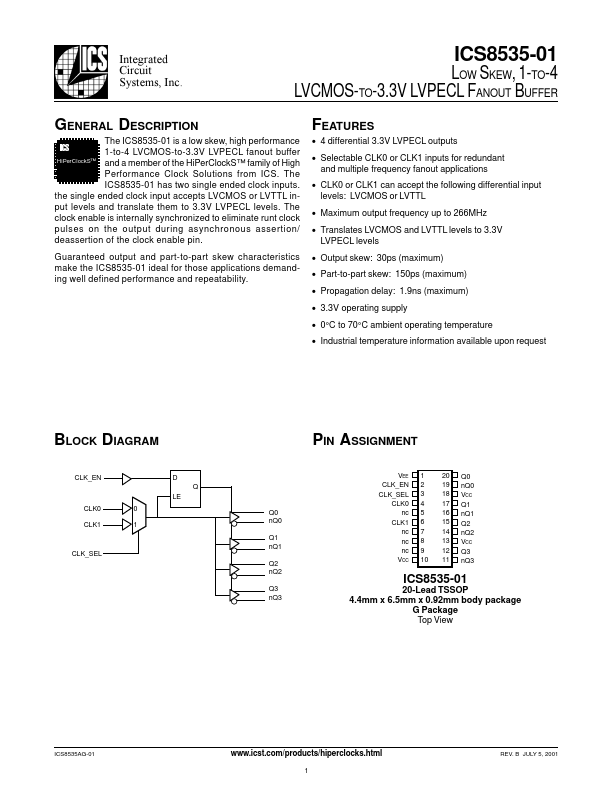

BLOCK DIAGRAM

CLK_EN D Q LE CLK0 CLK1 0 1 Q0 n Q0 Q1 n Q1 CLK_SEL Q2 n Q2 Q3 n Q3

PIN ASSIGNMENT

VEE CLK_EN CLK_SEL CLK0 nc CLK1 nc nc nc VCC 1 2 3 4 5 6 7 8 9 10 20 19 18 17 16 15 14 13 12 11 Q0 n Q0 VCC Q1 n Q1 Q2 n Q2 VCC Q3 n Q3

20-Lead TSSOP 4.4mm x 6.5mm x 0.92mm body package G Package Top View

ICS8535AG-01

.icst./products/hiperclocks.html

REV. B JULY 5, 2001

Integrated Circuit Systems, Inc.

LOW SKEW, 1-TO-4 LVCMOS-TO-3.3V LVPECL FANOUT BUFFER

Type Description Negative supply pin. Connect to ground. Synchronizing clock enable. When HIGH, clock outputs follow clock input. When LOW, Q outputs are...