9DBL09P1

9DBL09P1 is 9-Output 3.3V PCIe Fanout Buffer manufactured by IDT.

- Part of the 9DBL0941 comparator family.

- Part of the 9DBL0941 comparator family.

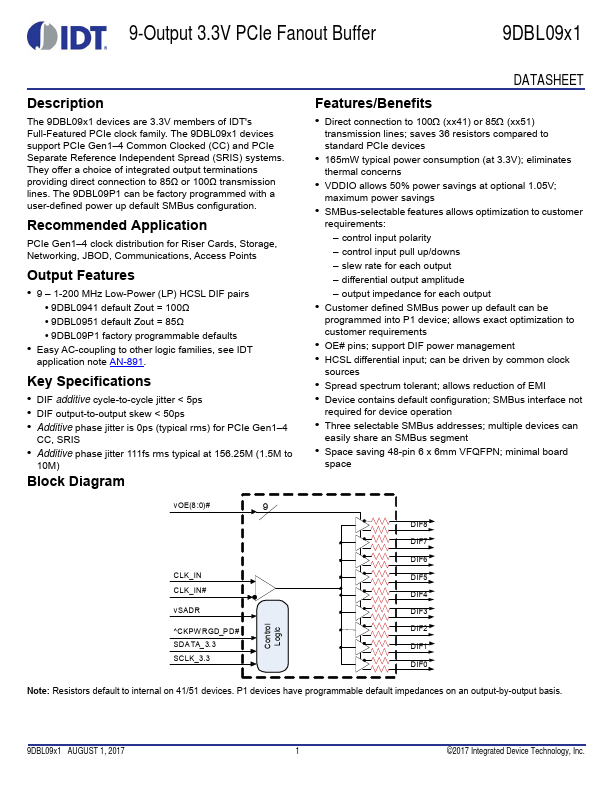

Description

The 9DBL09x1 devices are 3.3V members of IDT's Full-Featured PCIe clock family. The 9DBL09x1 devices support PCIe Gen1- 4 mon Clocked (CC) and PCIe Separate Reference Independent Spread (SRIS) systems. They offer a choice of integrated output terminations providing direct connection to 85Ω or 100Ω transmission lines. The 9DBL09P1 can be factory programmed with a user-defined power up default SMBus configuration.

Remended Application

PCIe Gen1- 4 clock distribution for Riser Cards, Storage, Networking, JBOD, munications, Access Points

Output Features

- 9

- 1-200 MHz Low-Power (LP) HCSL DIF pairs

- 9DBL0941 default Zout = 100Ω

- 9DBL0951 default Zout = 85Ω

- 9DBL09P1 factory programmable defaults

- Easy AC-coupling to other logic families, see IDT application note AN-891.

Key Specifications

- DIF additive cycle-to-cycle jitter < 5ps

- DIF output-to-output skew < 50ps

- Additive phase jitter is...