9FGL0841

9FGL0841 is 8-Output 3.3V PCIe Clock Generator manufactured by IDT.

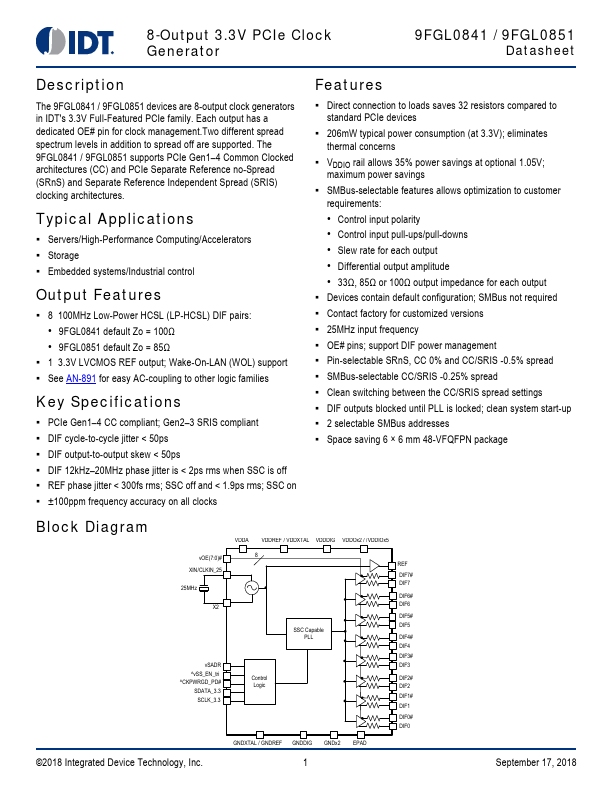

Description

The 9FGL0841 / 9FGL0851 devices are 8-output clock generators in IDT's 3.3V Full-Featured PCIe family. Each output has a dedicated OE# pin for clock management.Two different spread spectrum levels in addition to spread off are supported. The 9FGL0841 / 9FGL0851 supports PCIe Gen1- 4 mon Clocked architectures (CC) and PCIe Separate Reference no-Spread (SRn S) and Separate Reference Independent Spread (SRIS) clocking architectures.

Typical Applications

- Servers/High-Performance puting/Accelerators

- Storage

- Embedded systems/Industrial control

Output Features

- 8 100MHz Low-Power HCSL (LP-HCSL) DIF pairs:

- 9FGL0841 default Zo = 100Ω

- 9FGL0851 default Zo = 85Ω

- 1 3.3V LVCMOS REF output; Wake-On-LAN (WOL) support

- See AN-891 for easy AC-coupling to other logic families

Key Specifications

- PCIe Gen1- 4 CC pliant; Gen2- 3 SRIS pliant

- DIF cycle-to-cycle jitter <...