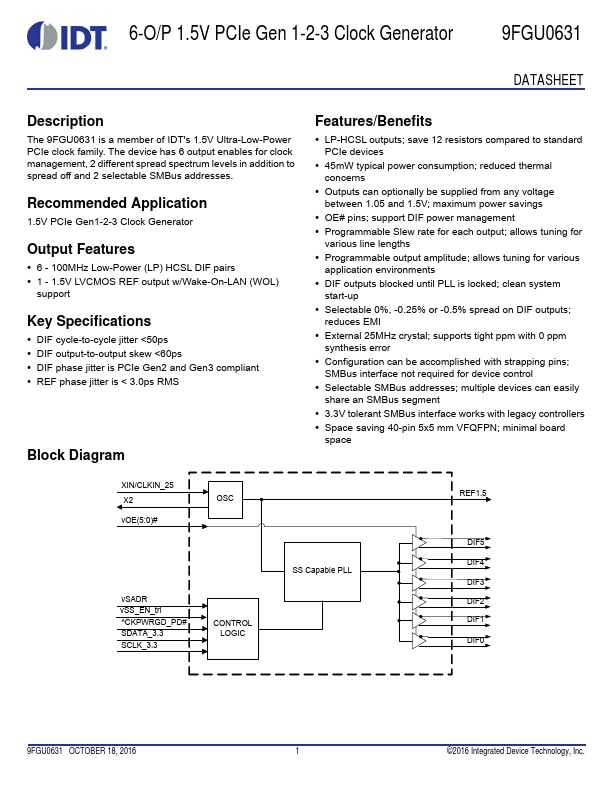

9FGU0631 Key Features

- 100MHz Low-Power (LP) HCSL DIF pairs

- 1.5V LVCMOS REF output w/Wake-On-LAN (WOL)

- DIF cycle-to-cycle jitter <50ps

- DIF output-to-output skew <60ps

- DIF phase jitter is PCIe Gen2 and Gen3 pliant

- REF phase jitter is < 3.0ps RMS

- LP-HCSL outputs; save 12 resistors pared to standard

- 45mW typical power consumption; reduced thermal

- Outputs can optionally be supplied from any voltage

- OE# pins; support DIF power management