ICS571 Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Pins: 8

Operating Voltage: 3.3 V

Description

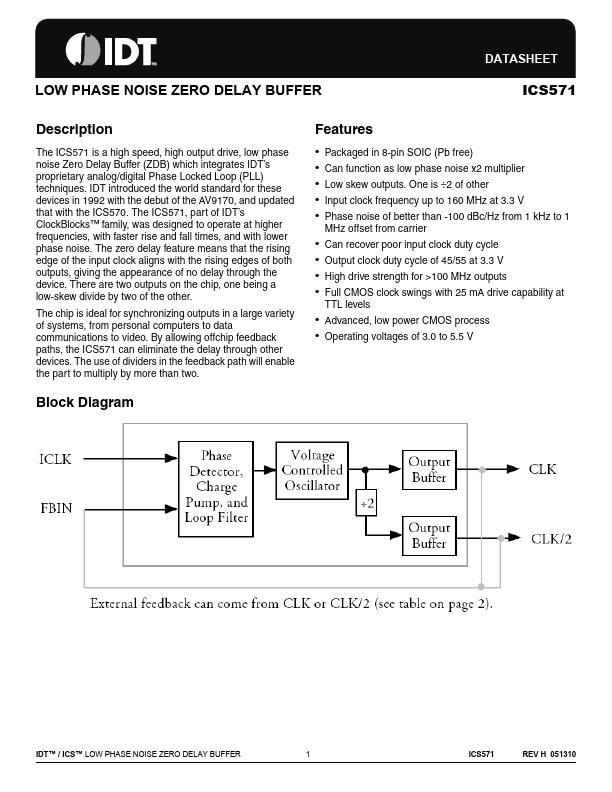

The ICS571 is a high speed, high output drive, low phase noise Zero Delay Buffer (ZDB) which integrates IDT’s proprietary analog/digital Phase Locked Loop (PLL) techniques. IDT introduced the world standard for these devices in 1992 with the debut of the AV9170, and updated that with the ICS570.

Key Features

- Packaged in 8-pin SOIC (Pb free)

- Can function as low phase noise x2 multiplier

- Low skew outputs. One is ÷2 of other

- Input clock frequency up to 160 MHz at 3.3 V

- Phase noise of better than -100 dBc/Hz from 1 kHz to 1 MHz offset from carrier