IDT23S08T Overview

Key Specifications

Package: SOIC

Mount Type: Surface Mount

Operating Voltage: 2.5 V

Max Voltage (typical range): 2.7 V

Key Features

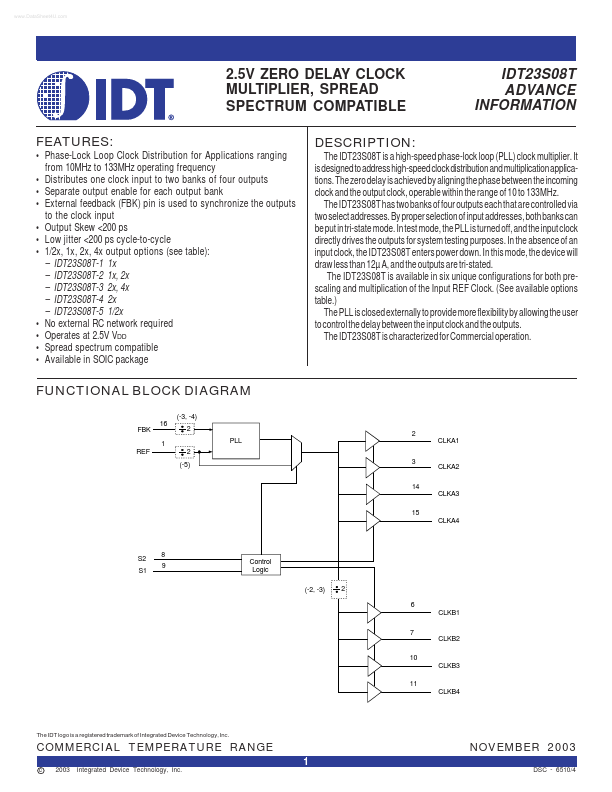

- Phase-Lock Loop Clock Distribution for Applications ranging from 10MHz to 133MHz operating frequency

- Distributes one clock input to two banks of four outputs