IS46LD16640A

IS46LD16640A is 1Gb Mobile LPDDR2 S4 SDRAM manufactured by ISSI.

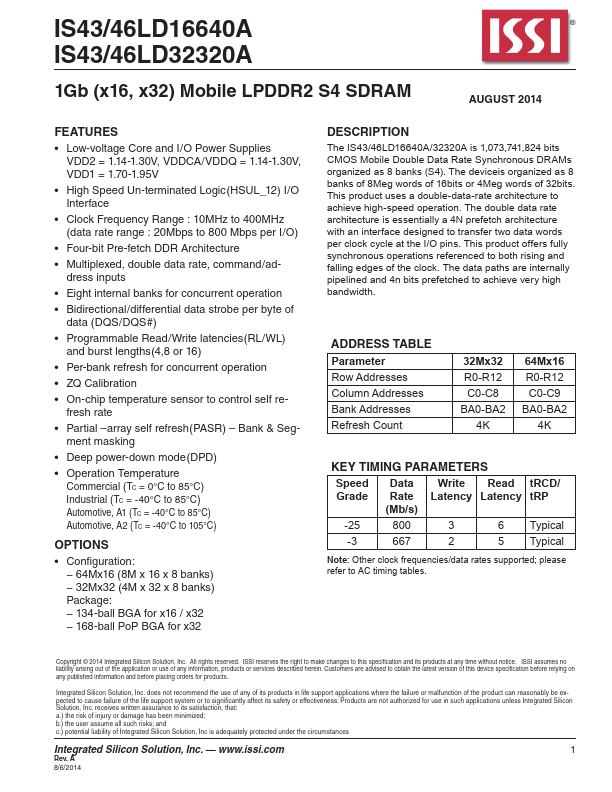

IS43/46LD16640A IS43/46LD32320A

1Gb (x16, x32) Mobile LPDDR2 S4 SDRAM

AUGUST 2014

Features

- Low-voltage Core and I/O Power Supplies VDD2 = 1.14-1.30V, VDDCA/VDDQ = 1.14-1.30V, VDD1 = 1.70-1.95V

- High Speed Un-terminated Logic(HSUL_12) I/O Interface

- Clock Frequency Range : 10MHz to 400MHz (data rate range : 20Mbps to 800 Mbps per I/O)

- Four-bit Pre-fetch DDR Architecture

- Multiplexed, double data rate, mand/address inputs

- Eight internal banks for concurrent operation

- Bidirectional/differential data strobe per byte of data (DQS/DQS#)

- Programmable Read/Write latencies(RL/WL) and burst lengths(4,8 or 16)

- Per-bank refresh for concurrent operation

- ZQ Calibration

-...