IS61SP12832

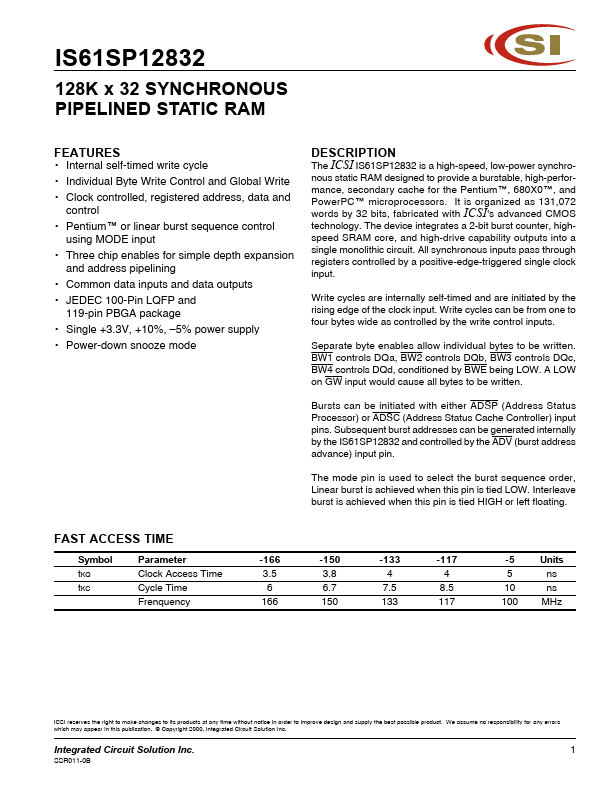

IS61SP12832 is 128K x 32 SYNCHRONOUS PIPELINED STATIC RAM manufactured by Integrated Circuit Solution.

128K x 32 SYNCHRONOUS PIPELINED STATIC RAM

Features

- Internal self-timed write cycle

- Individual Byte Write Control and Global Write

- Clock controlled, registered address, data and control

- Pentium™ or linear burst sequence control using MODE input

- Three chip enables for simple depth expansion and address pipelining

- mon data inputs and data outputs

- JEDEC 100-Pin LQFP and

119-pin PBGA package

- Single +3.3V, +10%,

- 5% power supply

- Power-down snooze mode

DESCRIPTION The ICSI IS61SP12832 is a high-speed, low-power synchro- nous static RAM designed to provide a burstable, high-performance, secondary cache for the Pentium™, 680X0™, and PowerPC™ microprocessors. It...