ICS650R-07C

ICS650R-07C is Networking Clock Source manufactured by Integrated Circuit Systems.

- Part of the ICS650-07C comparator family.

- Part of the ICS650-07C comparator family.

(

D a t a S h e e t

: w w w . D a t a S h e e t 4 U . c o m

)

PRELIMINARY INFORMATION

ICS650-07C Networking Clock Source

Description

The ICS650-07C is a low cost, low jitter, high performance clock synthesizer for networking applications. Using analog Phase-Locked Loop (PLL) techniques, the device accepts a 12.5 MHz or 25.00 MHz clock or fundamental mode crystal input to produce multiple output clocks for networking chips, PCI devices, SDRAM, and ASICs. The ICS650-07C outputs all have 0 ppm synthesis error. See the MK74CB214, ICS551, and ICS552-01 for non-PLL buffer devices which produce multiple low-skew copies of these output clocks. See the ICS570, ICS9112-16/17/18 for zero delay buffers that can synchronize outputs and other needed clocks.

Features

- Packaged in 20 pin narrow (150 mil) SSOP (QSOP)

- 12.5 MHz or 25.00 MHz fundamental crystal or clock input

- Six output clocks with selectable frequencies

- SDRAM frequencies of 67, 83, 100, and 133 MHz

- Buffered crystal reference output

- Zero ppm synthesis error in all clocks

- Ideal for PMC-Sierra’s ATM switch chips

- Full CMOS output swing with 25 m A output drive capability at TTL levels

- Advanced, low power, sub-micron CMOS process

- 3.0V to 5.5V operating voltage

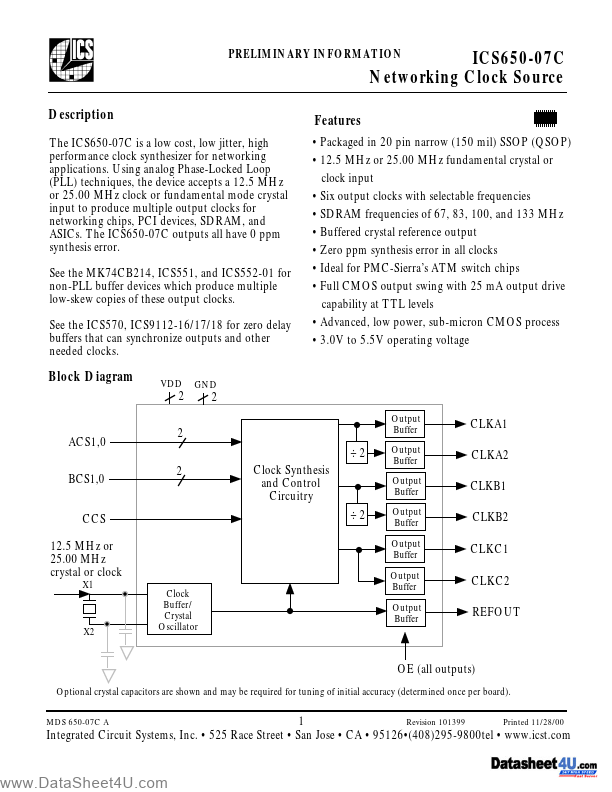

Block Diagram

2 2

Output Buffer

CLKA1 CLKA2 CLKB1 CLKB2 CLKC1 CLKC2 REFOUT

ACS1,0 BCS1,0 CCS 12.5 MHz or 25.00 MHz crystal or clock

X1

÷2 2 Clock Synthesis and Control Circuitry ÷2

Output Buffer Output Buffer Output Buffer Output Buffer Output Buffer Output Buffer

X2

Clock Buffer/ Crystal Oscillator

OE (all...