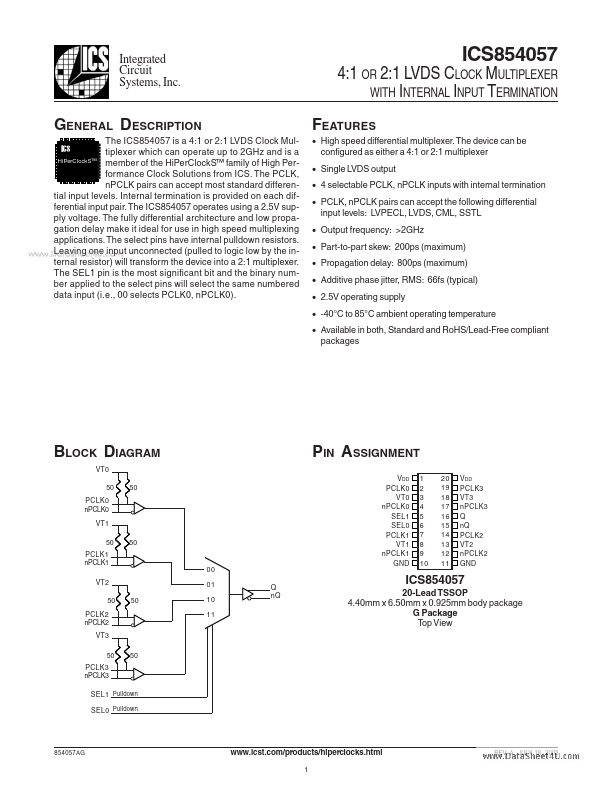

Datasheet Summary

Integrated Circuit Systems, Inc.

4:1 OR 2:1 LVDS CLOCK MULTIPLEXER WITH INTERNAL INPUT TERMINATION

Features

- High speed differential multiplexer. The device can be configured as either a 4:1 or 2:1 multiplexer

- Single LVDS output

- 4 selectable PCLK, nPCLK inputs with internal termination

- PCLK, nPCLK pairs can accept the following differential input levels: LVPECL, LVDS, CML, SSTL

- Output frequency: >2GHz

- Part-to-part skew: 200ps (maximum)

- Propagation delay: 800ps (maximum)

- Additive phase jitter, RMS: 66fs (typical)

- 2.5V operating supply

- -40°C to 85°C ambient operating temperature

- Available in both, Standard and RoHS/Lead-Free pliant packages

GENERAL...