ICS9248-134

ICS9248-134 is Frequency Generator & Integrated Buffers manufactured by Integrated Circuit Systems.

Integrated Circuit Systems, Inc.

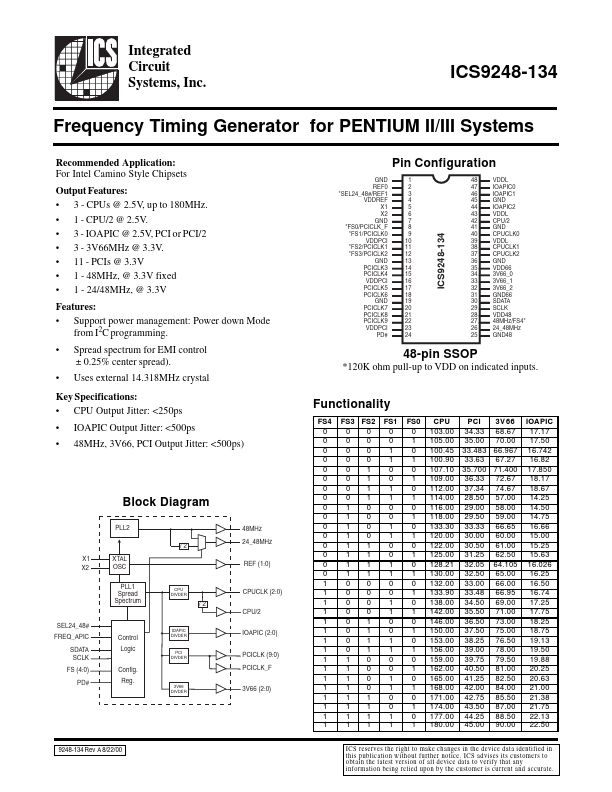

Frequency Timing Generator for PENTIUM II/III Systems

Remended Application: For Intel Camino Style Chipsets Output Features

:

- 3

- CPUs @ 2.5V, up to 180MHz.

- 1

- CPU/2 @ 2.5V.

- 3

- IOAPIC @ 2.5V, PCI or PCI/2

- 3

- 3V66MHz @ 3.3V.

- 11

- PCIs @ 3.3V

- 1

- 48MHz, @ 3.3V fixed

- 1

- 24/48MHz, @ 3.3V Features

:

- Support power management: Power down Mode from I2C programming.

- - Spread spectrum for EMI control ± 0.25% center spread). Uses external 14.318MHz crystal

Pin Configuration

GND REF0

- SEL24_48#/REF1 VDDREF X1 X2 GND

- FS0/PCICLK_F

- FS1/PCICLK0 VDDPCI

- FS2/PCICLK1

- FS3/PCICLK2 GND PCICLK3 PCICLK4 VDDPCI PCICLK5 PCICLK6 GND PCICLK7 PCICLK8 PCICLK9 VDDPCI PD# 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 VDDL IOAPIC0 IOAPIC1 GND IOAPIC2 VDDL CPU/2 GND CPUCLK0 VDDL CPUCLK1 CPUCLK2 GND VDD66 3V66_0 3V66_1 3V66_2 GND66 SDATA SCLK VDD48 48MHz/FS4- 24_48MHz GND48

48-pin SSOP

- 120K ohm pull-up to VDD on indicated...