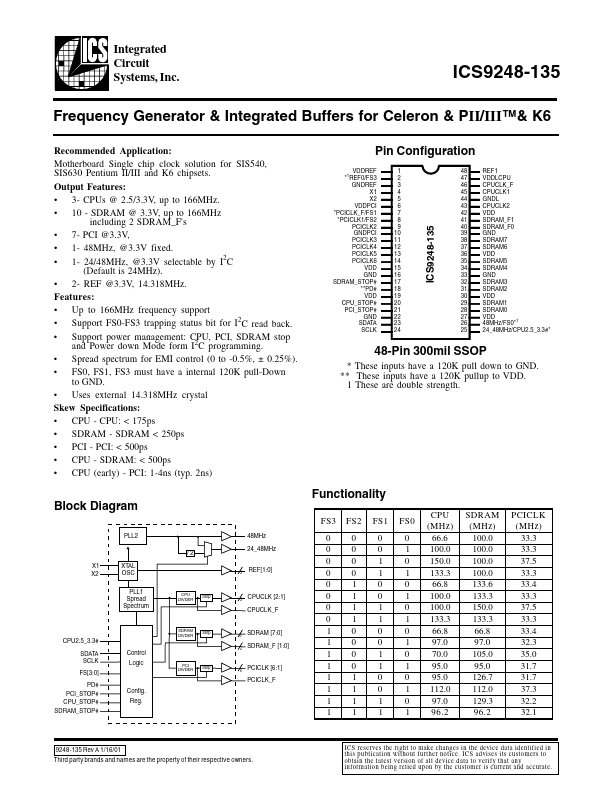

| Part | ICS9248-135 |

|---|---|

| Description | Frequency Generator & Integrated Buffers |

| Manufacturer | Integrated Circuit Systems |

| Size | 191.67 KB |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| ICS9248-80 | Renesas | General Purpose 133MHz System Clock |

| ICS9248-138 | Renesas | Frequency Generator & Integrated Buffer |