M1040 Overview

Description

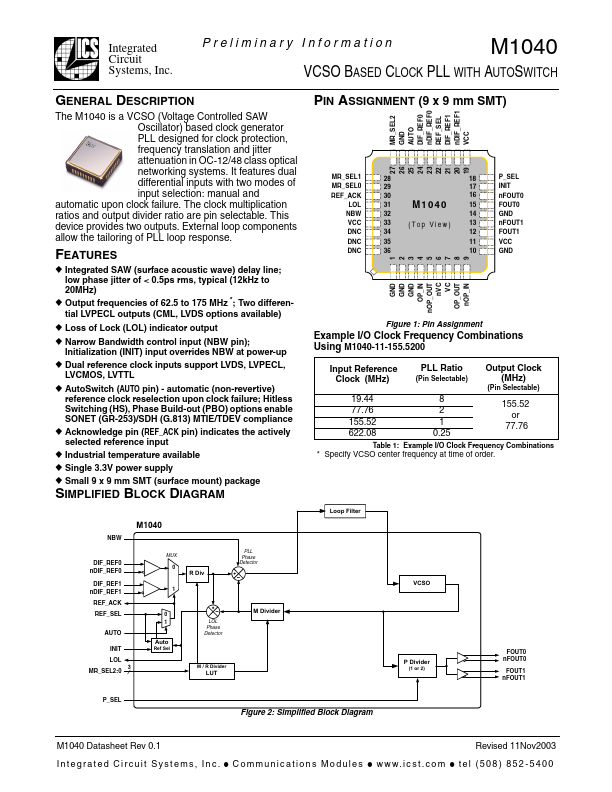

The M1040 is a VCSO (Voltage Controlled SAW Oscillator) based clock generator PLL designed for clock protection, frequency translation and jitter attenuation in OC-12/48 class optical networking systems. It features dual differential inputs with two modes of input selection: manual and automatic upon clock failure.

Key Features

- Integrated SAW (surface acoustic wave) delay line; low phase jitter of < 0.5ps rms, typical (12kHz to 20MHz)

- Output frequencies of 62.5 to 175 MHz *; Two differential LVPECL outputs (CML, LVDS options available)

- Loss of Lock (LOL) indicator output

- Narrow Bandwidth control input (NBW pin); Initialization (INIT) input overrides NBW at power-up

- Dual reference clock inputs support LVDS, LVPECL, LVCMOS, LVTTL

- AutoSwitch (AUTO pin)

- Acknowledge pin (REF_ACK pin) indicates the actively selected reference input

- Industrial temperature available

- Single 3.3V power supply