ICS831742I

ICS831742I is 4:2 Differential Clock/Data Multiplexer manufactured by Integrated Device Technology.

4:2 Differential Clock/Data Multiplexer

DATA SHEET

General Description

The ICS831742I is a high-performance, differential HCSL clock/data multiplexer and fanout buffer. The device is designed for the multiplexing and fanout of high-frequency clock and data signals. The device has four differential, selectable clock/data inputs. The selected input signal is distributed to two low-skew differential HCSL outputs. Each input pair accepts HCSL, LVDS and LVPECL levels. The ICS831742I is characterized to operate from a 3.3V power supply. Guaranteed input, output-to-output and part-to-part skew characteristics make the ICS831742I ideal for those clock and data distribution applications demanding well-defined performance and repeatability. The ICS831742I supports the clock multiplexing and distribution of PCI Express (2.5 Gb/s), Gen 2 (5 Gb/s) and Gen 3 (8 Gb/s) clock signals.

Features

- 4:2 differential clock/data multiplexer with fanout

- Four selectable, differential input pairs

- Each differential input pair can accept the following levels: HCSL,

LVDS and LVPECL

- Two differential HCSL output pairs

- Maximum input/output clock frequency: 700MHz

- Maximum input/output data rate: 1400Mb/s (NRZ)

- LVCMOS interface levels for all control inputs

- PCI Express (2.5Gb/s), Gen 2 (5 Gb/s) and Gen 3 (8 Gb/s) clock jitter pliant

- Input skew: 110ps max

- Part-to-part skew: 225ps max

- Full 3.3V supply voltage

- Available in lead-free (Ro HS 6)

- -40°C to 85°C ambient operating temperature

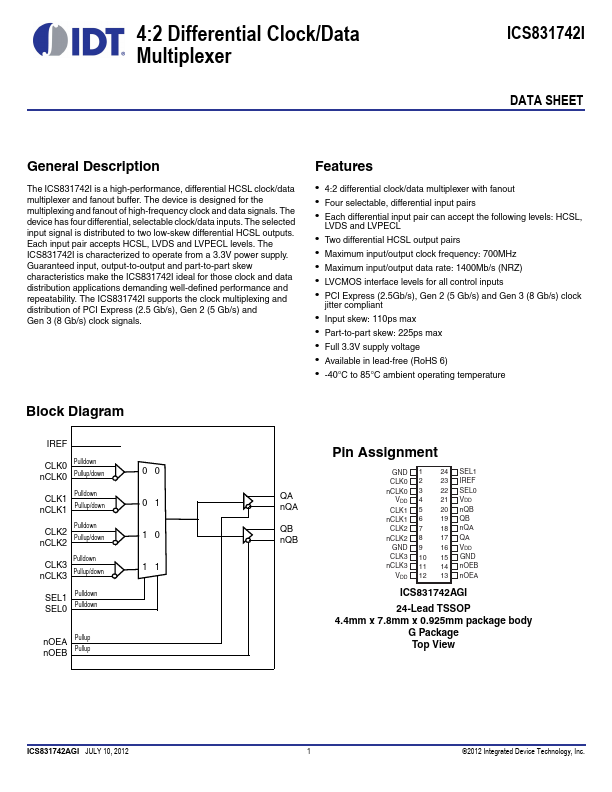

Block Diagram

IREF CLK0 Pulldown n CLK0 Pullup/down

Pulldown

CLK1 n CLK1 Pullup/down

Pulldown

CLK2 n CLK2 Pullup/down

Pulldown

CLK3 n CLK3 Pullup/down

SEL1 Pulldown SEL0 Pulldown n OEA Pullup n OEB Pullup

00 01 10 11

QA n...