IDT72T40108

IDT72T40108 is HIGH-SPEED TeraSync DDR/SDR FIFO manufactured by Integrated Device Technology.

..

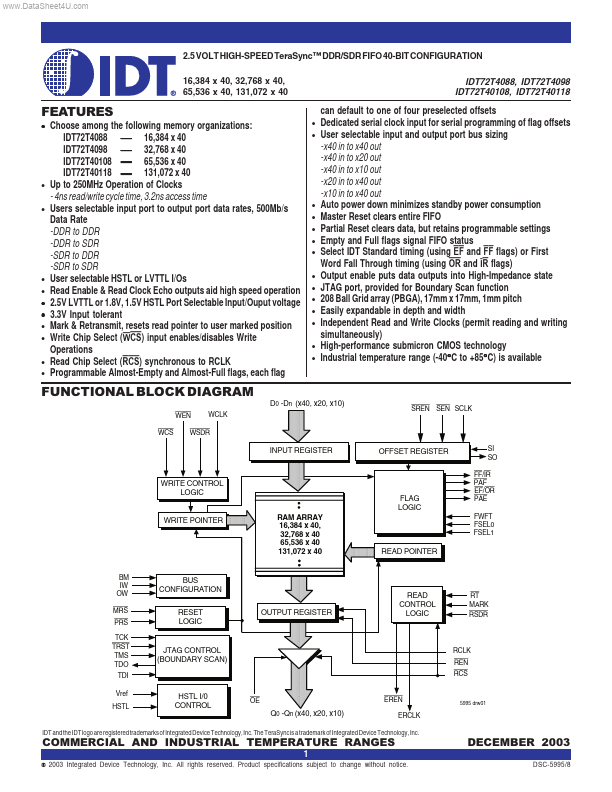

2.5 VOLT HIGH-SPEED TeraSync™ DDR/SDR FIFO 40-BIT CONFIGURATION 16,384 x 40, 32,768 x 40, 65,536 x 40, 131,072 x 40

IDT72T4088, IDT72T4098 IDT72T40108, IDT72T40118

- -

Features

- -

- -

- -

- -

- -

- Choose among the following memory organizations: IDT72T4088 16,384 x 40 IDT72T4098 32,768 x 40 IDT72T40108 65,536 x 40 IDT72T40118 131,072 x 40 Up to 250MHz Operation of Clocks

- 4ns read/write cycle time, 3.2ns access time Users selectable input port to output port data rates, 500Mb/s Data Rate -DDR to DDR -DDR to SDR -SDR to DDR -SDR to SDR User selectable HSTL or LVTTL I/Os Read Enable & Read Clock Echo outputs aid high speed operation 2.5V LVTTL or 1.8V,...