V103

Description

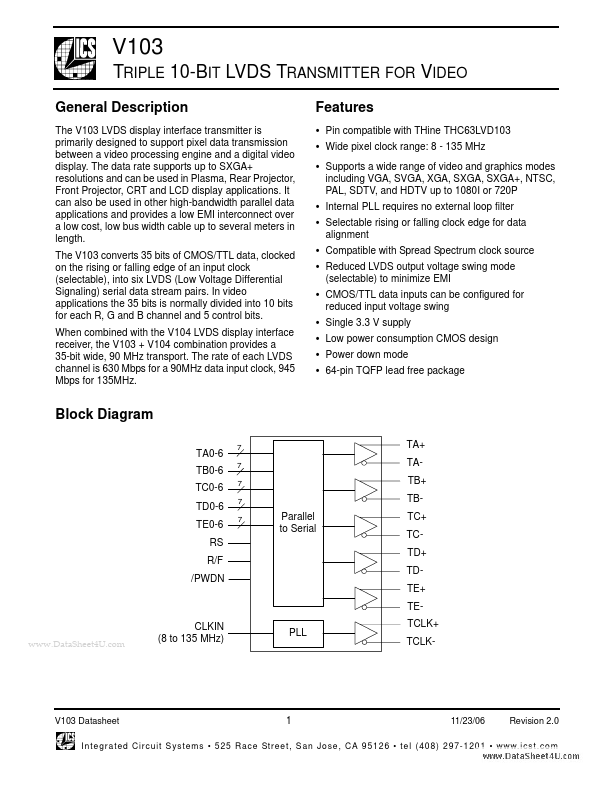

The V103 LVDS display interface transmitter is primarily designed to support pixel data transmission between a video processing engine and a digital video display.

Key Features

- Wide pixel clock range: 8 - 135 MHz

- Supports a wide range of video and graphics modes including VGA, SVGA, XGA, SXGA, SXGA+, NTSC, PAL, SDTV, and HDTV up to 1080I or 720P

- Internal PLL requires no external loop filter

- Selectable rising or falling clock edge for data alignment

- Reduced LVDS output voltage swing mode (selectable) to minimize EMI

- CMOS/TTL data inputs can be configured for reduced input voltage swing

- Single 3.3 V supply Low power consumption CMOS design Power down mode 64-pin TQFP lead free package