IS42R32200C1 Description

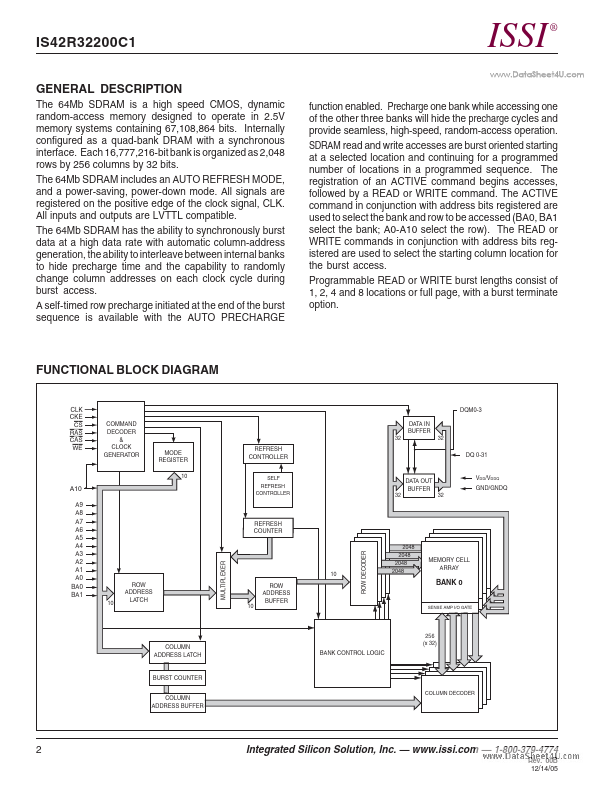

The 64Mb SDRAM is a high speed CMOS, dynamic random-access memory designed to operate in 2.5V memory systems containing 67,108,864 bits. Internally configured as a quad-bank DRAM with a synchronous interface. Each 16,777,216-bit bank is organized as 2,048 rows by 256 columns by 32 bits.

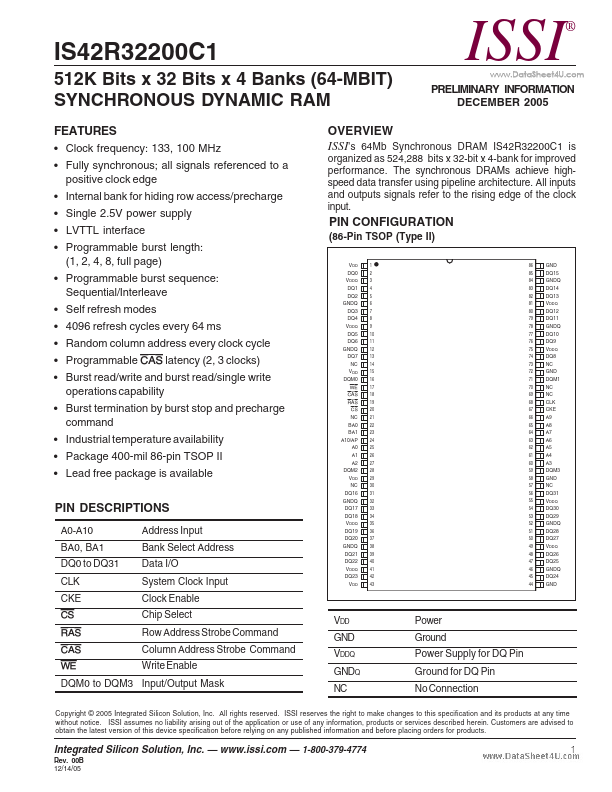

IS42R32200C1 Key Features

- Clock frequency: 133, 100 MHz

- Fully synchronous; all signals referenced to a positive clock edge

- Internal bank for hiding row access/precharge

- Single 2.5V power supply

- LVTTL interface

- Programmable burst length: (1, 2, 4, 8, full page)

- Programmable burst sequence: Sequential/Interleave

- Self refresh modes

- 4096 refresh cycles every 64 ms

- Random column address every clock cycle