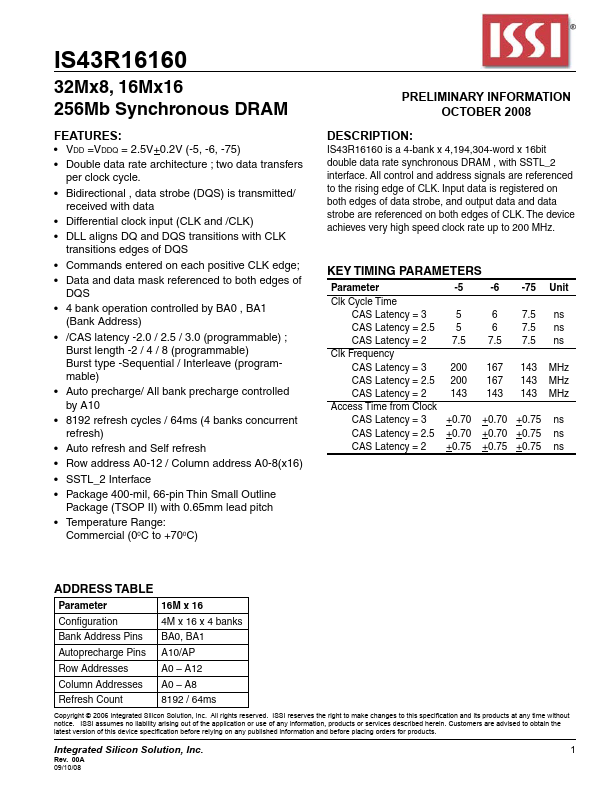

IS43R16160 Overview

Key Specifications

Package: TSSOP

Pins: 66

Operating Voltage: 2.5 V

Max Voltage (typical range): 2.7 V

Description

IS43R16160 is a 4-bank x 4,194,304-word x 16bit double data rate synchronous DRAM , with SSTL_2 interface. All control and address signals are referenced to the rising edge of CLK.

Key Features

- Double data rate architecture ; two data transfers per clock cycle

- Bidirectional , data strobe (DQS) is transmitted/ received with data

- Differential clock input (CLK and /CLK)

- DLL aligns DQ and DQS transitions with CLK transitions edges of DQS

- Commands entered on each positive CLK edge