ACS10MS

Overview

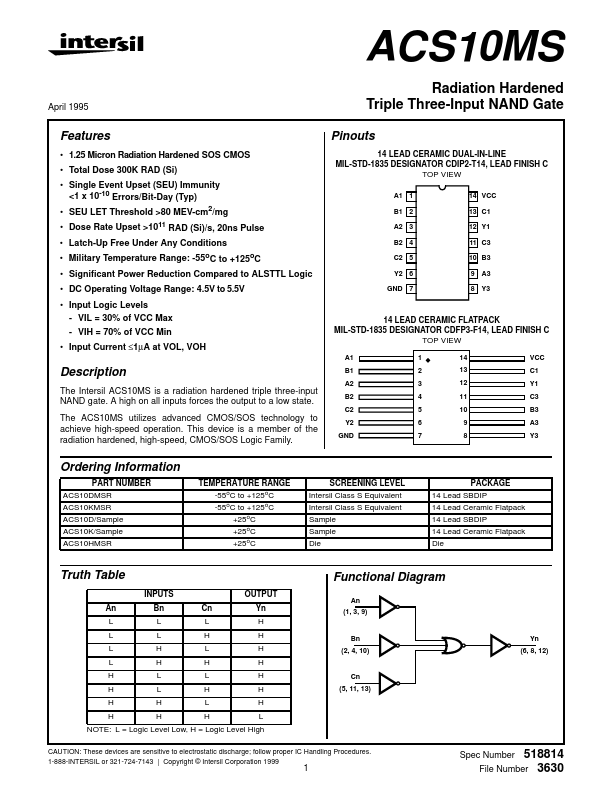

The Intersil ACS10MS is a radiation hardened triple three-input NAND gate. A high on all inputs forces the output to a low state.

- 1.25 Micron Radiation Hardened SOS CMOS

- Total Dose 300K RAD (Si)

- Single Event Upset (SEU) Immunity <1 x 10-10 Errors/Bit-Day (Typ)

- SEU LET Threshold >80

- Dose Rate Upset >1011 MEV-cm2 /mg RAD (Si)/s, 20ns Pulse -55oC +125oC

- Latch-Up Free Under Any Conditions

- Military Temperature Range: to