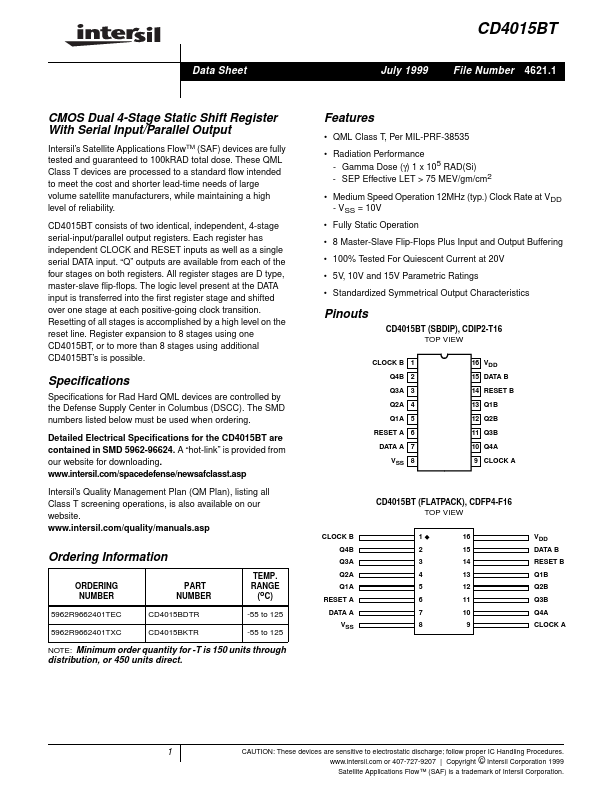

- Part: CD4015BT

- Description: CMOS Dual 4-Stage Static Shift Register

- Manufacturer: Intersil

- Size: 74.25 KB

Datasheets by Manufacturer

- CD4015B — RCA — CMOS Dual 4-Stage Static Shift Register

- CD4015BM — Texas Instruments — CMOS Dual 4-Stage Static Shift Register

- CD4015BF3A — Texas Instruments — CMOS Dual 4-Stage Static Shift Register

- CD4015BF — Texas Instruments — CMOS Dual 4-Stage Static Shift Register

- CD4019B — RCA — CMOS Quad AND/OR Select Gate

- CD4018B — RCA — CMOS PRESETTABLE DIVIDE-BY-N COUNTER

- CD4016B — RCA — CMOS Quad Bilateral Switch

- CD4011B — RCA — CMOS NAND Gates

- CD40101B — RCA — CMOS 9-Bit Parity Generator/Checker

- CD40103B — RCA — CMOS 8-Stage Presettable Synchronous Down Counters