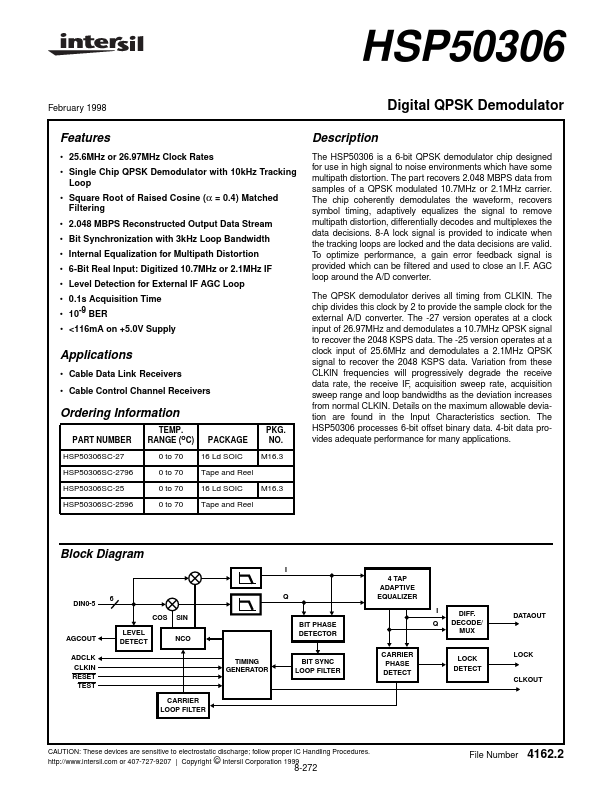

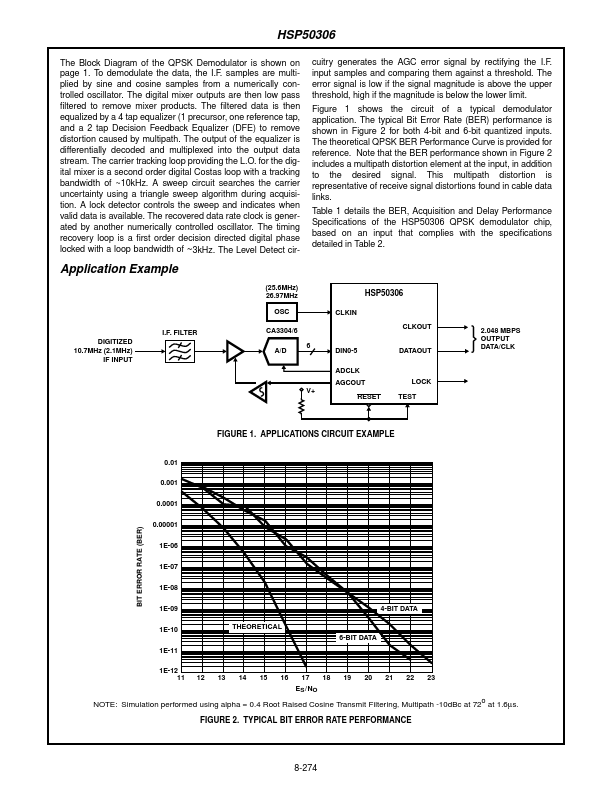

HSP50306 Key Features

- 25.6MHz or 26.97MHz Clock Rates

- Single Chip QPSK Demodulator with 10kHz Tracking Loop

- Square Root of Raised Cosine (α = 0.4) Matched Filtering

- 2.048 MBPS Reconstructed Output Data Stream

- Bit Synchronization with 3kHz Loop Bandwidth

- Internal Equalization for Multipath Distortion

- 6-Bit Real Input: Digitized 10.7MHz or 2.1MHz IF

- Level Detection for External IF AGC Loop

- 0.1s Acquisition Time

- 10-9 BER