HCS109MS Datasheet Text

HCS109MS

Radiation Hardened Dual JK Flip Flop

Features

- 3 Micron Radiation Hardened SOS CMOS

- Total Dose 200K RAD (Si)

- SEP Effective LET No Upsets: >100 MEV-cm2/mg

- Single Event Upset (SEU) Immunity < 2 x 10-9 Errors/

Bit-Day (Typ)

- Dose Rate Survivability: >1 x 1012 RAD (Si)/s

- Dose Rate Upset >1010 RAD (Si)/s 20ns Pulse

- Cosmic Ray Upset Immunity < 2 x 10-9 Errors/Bit-Day

(Typ)

- Latch-Up Free Under Any Conditions

- Military Temperature Range: -55oC to +125oC

- Significant Power Reduction pared to LSTTL ICs

- DC Operating Voltage Range: 4.5V to 5.5V

- Input Logic Levels

- VIL = 30% of VCC Max

- VIH = 70% of VCC Min

- Input Current Levels Ii 5A at VOL, VOH

Description

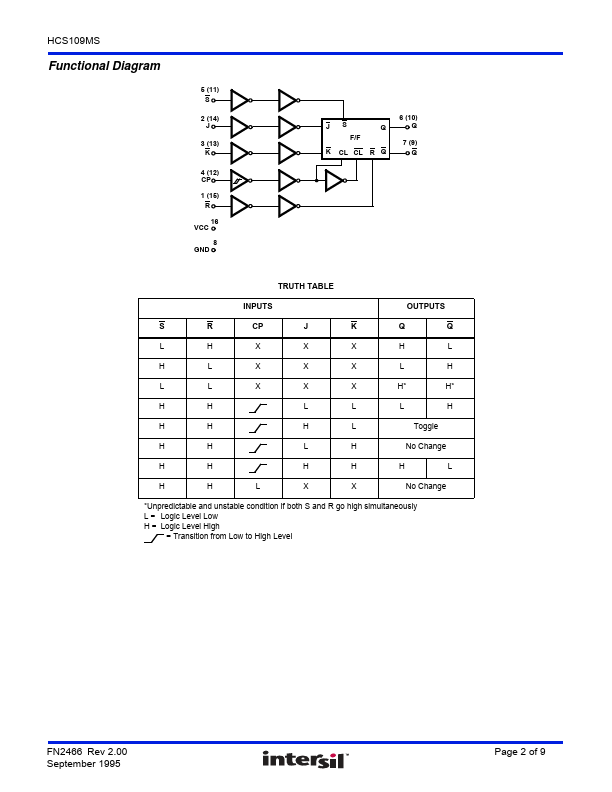

The Intersil HCS109MS is a Radiation Hardened Dual JK Flip Flop with set and reset. The flip flop changes state with the positive transition of the clock (CP1 or CP2). The HCS109MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of radiation hardened, high-speed, CMOS/SOS Logic Family. The HCS109MS is supplied in a 16 lead Ceramic flatpack (K suffix) or a SBDIP Package (D suffix).

DATASHEET

FN2466 Rev 2.00 September 1995

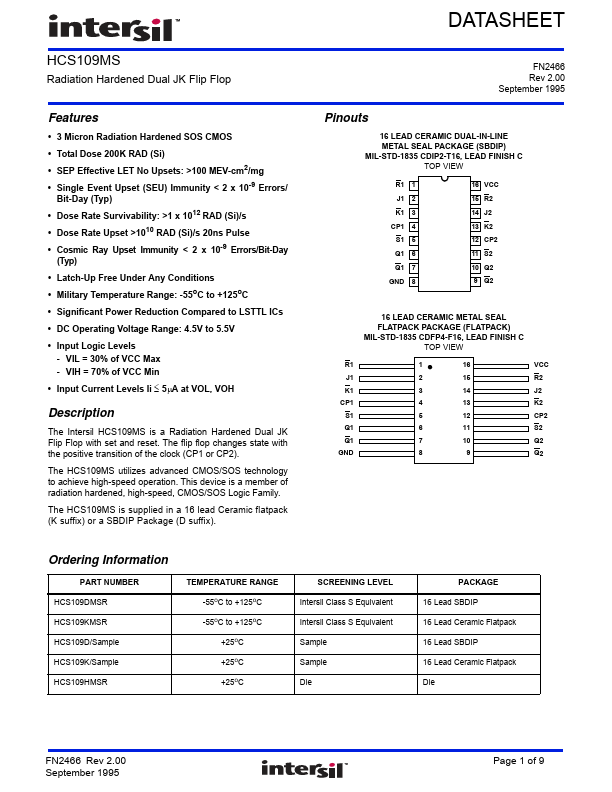

Pinouts

16 LEAD CERAMIC DUAL-IN-LINE METAL SEAL PACKAGE (SBDIP) MIL-STD-1835 CDIP2-T16, LEAD FINISH C

TOP VIEW

R1 1 J1 2 K1 3 CP1 4 S1 5 Q1 6 Q1 7 GND 8

16 VCC 15 R2 14 J2 13 K2 12 CP2 11 S2 10 Q2 9 Q2

16 LEAD CERAMIC METAL SEAL FLATPACK PACKAGE (FLATPACK) MIL-STD-1835 CDFP4-F16, LEAD FINISH C...