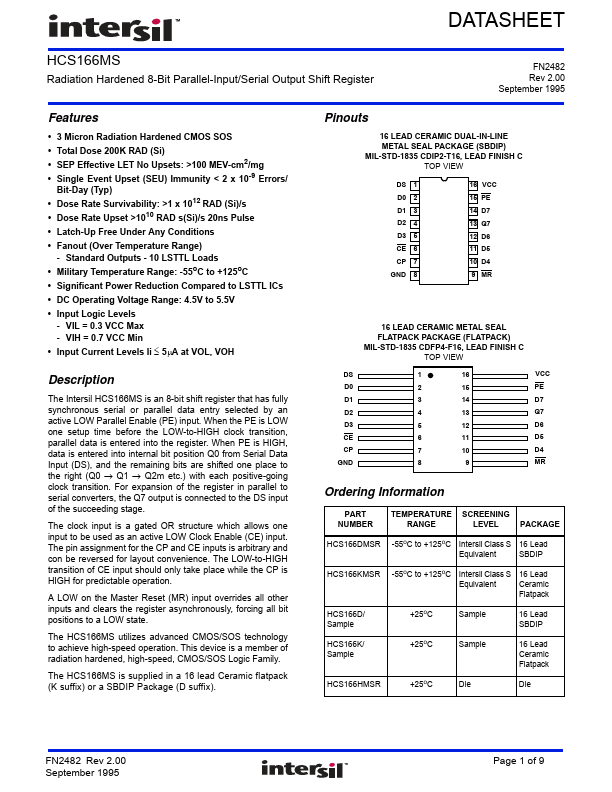

HCS166MS

HCS166MS is Radiation Hardened 8-Bit Parallel-Input/Serial Output Shift Register manufactured by Intersil.

Radiation Hardened 8-Bit Parallel-Input/Serial Output Shift Register

FN2482 Rev 2.00 September 1995

Features

- 3 Micron Radiation Hardened CMOS SOS

- Total Dose 200K RAD (Si)

- SEP Effective LET No Upsets: >100 MEV-cm2/mg

- Single Event Upset (SEU) Immunity < 2 x 10-9 Errors/

Bit-Day (Typ)

- Dose Rate Survivability: >1 x 1012 RAD (Si)/s

- Dose Rate Upset >1010 RAD s(Si)/s 20ns Pulse

- Latch-Up Free Under Any Conditions

- Fanout (Over Temperature Range)

- Standard Outputs

- 10 LSTTL Loads

- Military Temperature Range: -55o C to +125o C

- Significant Power Reduction pared to LSTTL ICs

- DC Operating Voltage Range: 4.5V to 5.5V

- Input Logic Levels

- VIL = 0.3 VCC Max

- VIH = 0.7 VCC Min

- Input Current Levels Ii 5A at VOL, VOH

Description

The Intersil HCS166MS is an 8-bit shift register that has fully synchronous serial or parallel data entry selected by an active LOW Parallel Enable (PE) input. When the PE is LOW one setup time before the LOW-to-HIGH clock transition, parallel data is entered into the register. When PE is HIGH, data is entered into internal bit position Q0 from Serial Data Input (DS), and the remaining bits are shifted one place to the right (Q0 Q1 Q2m etc.) with each positive-going clock transition. For expansion of the register in parallel to serial converters, the Q7 output is connected to the DS input of the succeeding stage.

The clock input is a gated OR structure which allows one input to be used as an active LOW Clock Enable (CE) input. The pin assignment for the CP and CE inputs is arbitrary and con be reversed for layout convenience. The LOW-to-HIGH transition of CE input should only take place while the CP is HIGH for predictable operation.

A LOW on the Master Reset (MR) input overrides all other inputs and clears the register asynchronously, forcing all bit positions to a LOW state.

The HCS166MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of radiation...