ISLA112P25M Description

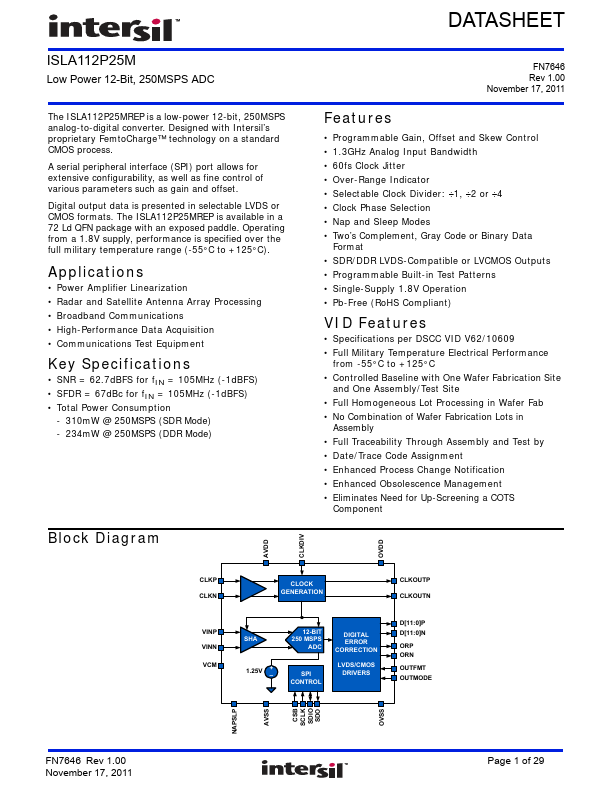

ISLA112P25M Low Power 12-Bit, 250MSPS ADC The ISLA112P25MREP is a low-power 12-bit, 250MSPS analog-to-digital converter. Designed with Intersil’s proprietary FemtoCharge™ technology on a standard CMOS process. A serial peripheral interface (SPI) port allows for extensive configurability, as well as fine control of various parameters such as gain and offset.

ISLA112P25M Key Features

- Programmable Gain, Offset and Skew Control

- 1.3GHz Analog Input Bandwidth

- 60fs Clock Jitter

- Over-Range Indicator

- Selectable Clock Divider: 1, 2 or 4

- Clock Phase Selection

- Nap and Sleep Modes

- Two’s plement, Gray Code or Binary Data

- SDR/DDR LVDS-patible or LVCMOS Outputs

- Programmable Built-in Test Patterns