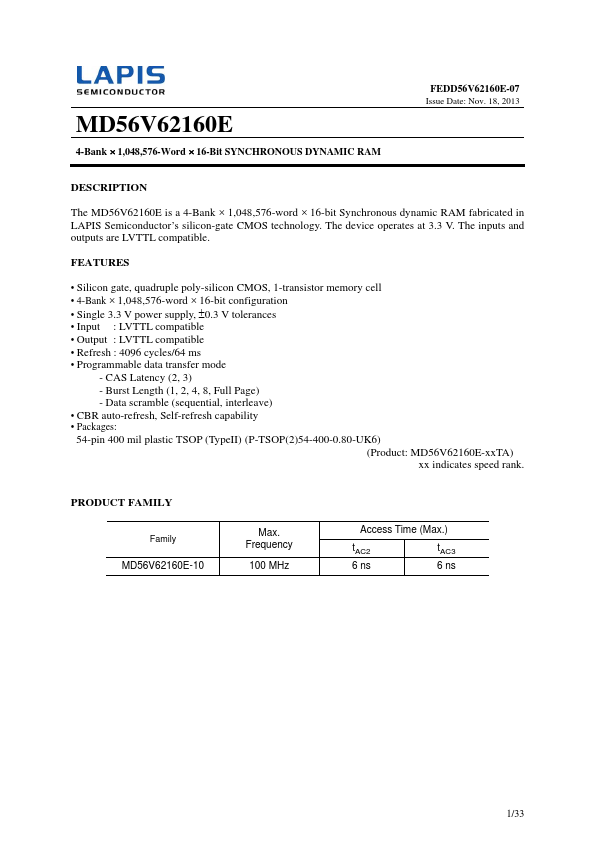

MD56V62160E

Description

The MD56V62160E is a 4-Bank 1,048,576-word 16-bit Synchronous dynamic RAM fabricated in LAPIS Semiconductor’s silicon-gate CMOS technology.

Key Features

- Silicon gate, quadruple poly-silicon CMOS, 1-transistor memory cell

- Single 3.3 V power supply, 0.3 V tolerances

- Refresh : 4096 cycles/64 ms

- Programmable data transfer mode

- CAS Latency (2, 3) - Burst Length (1, 2, 4, 8, Full Page) - Data scramble (sequential, interleave)

- CBR auto-refresh, Self-refresh capability