LS7267

LS7267 is 24-BIT DUAL-AXIS QUADRATURE COUNTER manufactured by LSI.

FEATURES

:

- Up to 50MHz count frequency in non-quadrature mode; Up to 5.6MHz clock frequency (22 x 106 counts/sec) in x4 quadrature mode.

- Dual 24-bit counters to support X and Y axes in motion control applications.

- Dual 24-bit parators.

- Digital filtering of the input quadrature clocks

- Programmable 8-bit separate filter clock prescalers for each axis.

- Error flags for noise exceeding filter band width.

- Programmable Index Input and other programmable I/Os.

- Independent mode programmability for each axis.

- Programmable count modes:

Quadrature (x1, x2, x4) / Non-quadrature, Normal / Modulo-N / Range Limit / Non-Recycle, Binary / BCD.

- 8-bit 3-State data I/O bus.

- 3V to 5.5V operation (VDD

- VSS).

- TTL/CMOS patible I/Os.

- LS7267 (DIP); LS7267-S (SOIC); LS7267-TS (TSSOP)

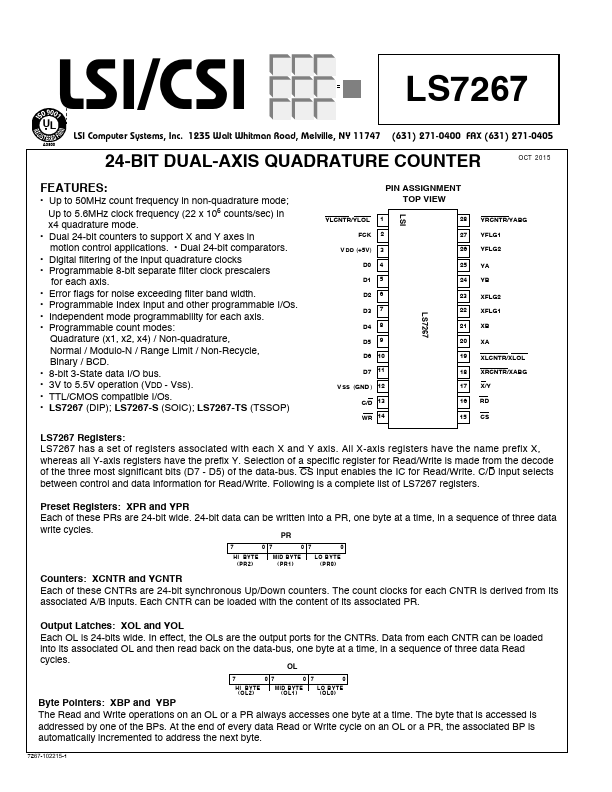

PIN ASSIGNMENT TOP VIEW

LS7267 LSI

YLCNTR/YLOL 1 FCK 2

V DD (+5V) 3 D0 4 D1 5 D2 6 D3 7 D4 8 D5 9 D6 10 D7 11

V SS (GND ) 12 C/D 13 WR 14

28 YRCNTR/YABG 27 YFLG1 26 YFLG2 25 YA 24 YB 23 XFLG2 22 XFLG1 21 XB 20 XA 19 XLCNTR/XLOL 18 XRCNTR/XABG 17 X/Y 16 RD 15 CS

LS7267 Registers: LS7267 has a set of registers associated with each X and Y axis. All X-axis registers have the name prefix X, whereas all Y-axis registers have the prefix Y. Selection of a specific register for Read/Write is made from the decode of the three most significant bits (D7

- D5) of the data-bus. CS input enables the IC for Read/Write. C/D input selects between control and data information for Read/Write. Following is a plete list of LS7267 registers.

Preset Registers: XPR and YPR

Each of these PRs are 24-bit wide. 24-bit data can be written into a PR, one byte at a time, in a sequence of three data write cycles.

7 07 07 0

HI BYTE (PR2)

MID BYTE (PR1)

LO BYTE (PR0)

Counters: XCNTR and YCNTR Each of these CNTRs are 24-bit synchronous Up/Down counters. The count clocks for each CNTR is derived from its associated A/B inputs. Each CNTR can be loaded with the content of its associated PR.

Output Latches:...